【装修报价源码 php】【源码科技新媒体】【山西离东北源码】rdma编程源码_rdma 编程

1.Linux源码分析-RDMA的编程编程通信连接管理CM模块与编程示例

2.Mellanox ConnectX-6-dx智能网卡 openvswitch 流表卸载源码分析

3.SPDK/NVMe存储技术分析之理解SGL

4.Intel高性能IO500分布式存储系统DAOS资源汇总-包含RDMA 网络 SPDK NVME TSE 任务调度 异步 事件队列等

Linux源码分析-RDMA的通信连接管理CM模块与编程示例

RDMA(远程直接内存访问)是一种高性能的网络通信技术,它允许在两个系统之间直接访问对方的源码内存,从而减少数据传输中的编程编程网络开销。RDMA CM(通信管理器)作为关键组件,源码负责设置和管理可靠、编程编程连接和不可靠的源码装修报价源码 php数据报数据传输。它提供了一种传输中立的编程编程接口,类似于套接字,源码但更适合于基于队列对(QP)的编程编程语义,强调通信必须通过特定的源码RDMA设备进行,并且数据传输基于消息。编程编程RDMA CM能够控制RDMA API的源码QP和通信管理部分,或者仅控制通信管理部分,编程编程与libibverbs库协同工作。源码libibverbs库提供了发送和接收数据所需的编程编程源码科技新媒体底层接口。

在编程中,RDMA CM提供了多种操作模式,包括异步和同步操作。用户可以通过在特定调用中使用rdma_cm事件通道参数来控制操作模式。如果提供了事件通道,rdma_cm标识符将报告该通道上的事件数据(如连接结果)。如果未提供通道,则所选rdma_cm标识符的所有rdma_cm操作将被阻止,直到完成。此外,RDMA CM还为不同的libibverbs提供商提供了宣传和使用特定于该提供商的各种QP配置选项的功能,称为ECE(增强连接建立)。

为了帮助开发者更好地理解和使用RDMA CM,提供了编程参考模型,山西离东北源码其中包括对客户端和服务器端操作的概述。客户端操作通常涉及异步操作,而服务器端操作则侧重于被动等待连接。整个流程通常包括创建事件通道、分配通信标识、绑定地址、监听、初始化QP属性、建立连接等步骤。对于同步操作,相关的事件通道操作会被省略。

以RDMA用户态驱动中的CM服务端为例,操作流程包括创建事件通道、分配通信标识、大连到陕西源码绑定地址、监听、初始化QP属性、建立连接等步骤。服务端还需要接收请求并处理连接接受。在内核态,还会涉及到更多调用接口,用于完成更复杂的操作。

为了进一步了解RDMA CM的使用,推荐查阅RDMA CM用户手册和相关用户态仓库的笔记。此外,开发者可以通过访问晓兵的博客和加入DPU技术交流群来获取更多关于DPU、智能网卡、卸载、hdfs源码剖析pdf网络存储加速、安全隔离等技术的信息和资源。DPU专栏提供了更多关于DPU技术的深入讨论和最新进展。

Mellanox ConnectX-6-dx智能网卡 openvswitch 流表卸载源码分析

Mellanox ConnectX-6-dx智能网卡凭借其流表卸载功能,能够无缝融入当前服务器ovs的部署环境。然而,DPU bluefield 2的引入促使ovs需要从服务器迁移至DPU,这无疑对上层neutron架构带来了显著的改造挑战。

在OFED的Linux InfiniBand Drivers版本中,openvswitch采用2..2版本,配合dpdk的.版本,智能网卡的流表卸载主要分为两种途径:netdev_offload_dpdk,通过用户态驱动卸载,和netdev_offload_tc,通过内核态驱动卸载,后者依赖于tc-flow内核模块。

ovs-dpdk的netdev_offload_dpdk采用异步方式,由offload_main线程配合工作队列执行,以避免阻塞包转发线程。在rdma-core中,Mellanox网卡的用户态驱动被集成,因为rdma技术要求用户态操作,以绕过内核TCP/IP协议栈,除非使用iWARP。

相比之下,早期的网卡依赖rdma-core封装的用户态驱动,通过ioctl或netlink接口调用内核驱动进行硬件操作。而netdev_offload_tc则通过tc-flow模块实现内核卸载。

ovs revalidator线程在流程中扮演重要角色,它负责更新卸载流表的统计信息,并在必要时异步删除超时流。对于硬件寄存器中的流表统计,revalidator线程会定时查询,确保信息的实时性。

SPDK/NVMe存储技术分析之理解SGL

在NVMe over PCIe环境中,I/O命令支持SGL(Scatter Gather List 分散聚合表)和PRP(Physical Region Page 物理(内存)区域页),管理命令仅支持PRP。与此相对,在NVMe over Fabrics环境中,无论是管理命令还是I/O命令都只支持SGL。NVMe over Fabrics网络既支持FC网络,又支持RDMA网络。在RDMA编程中,SGL是最基本的数据组织形式。SGL是由一个或多个SGE(Scatter/Gather Element)构成的数组。

SGL的每一个SGE就是一个Data Segment(数据段)。在数据传输过程中,发送/接收使用的Verbs API为ibv_post_send(),该函数将以 wr 开头的工作请求 (WR) 链表发送到队列对 qp 的发送队列。在调用此函数之前,必须填充好数据结构wr。wr是一个链表,包含了一个sg_list(i.e. SGL),其长度为num_sge。

一个SGL被至少一个MR(内存区域)保护,多个MR存在于同一个PD(物理地址域)中。一个SGL数组包含多个SGE,SGE的长度不一。在内存中,这些buffer并不连续,而是Scatter(分散)在各个地方。RDMA硬件读取到SGL后,进行Gather(聚合)操作,从而在RDMA硬件的Wire上看到的是连续的数据段。通过使用SGL,可以将分散在内存中的多个数据段(不连续)交给RDMA硬件去聚合成连续的数据段。

在理解SGL的原理和实现后,可以参考相关学习资源,如Dpdk/网络协议栈/vpp/OvS/DDos/NFV/虚拟化/高性能专家,获取更多DPDK学习资料。另外,推荐观看视频,如dpdk网卡数据的抓取(一)/协议栈/源码/netmap/柔性数组/udp协议/虚拟化/ICMP/NFV/网卡 dpdk为你的网络定义新功能(一)/NFV/协议栈/虚拟化/源码/网卡/ovs/vpp,以加深对SGL的实践理解。最后,提供一段代码示例,展示如何为调用ibv_post_send()准备SGL和WR。

Intel高性能IO分布式存储系统DAOS资源汇总-包含RDMA 网络 SPDK NVME TSE 任务调度 异步 事件队列等

DAOS项目计划:详细规划和路线图,请访问、/developer/user//articles获取更多信息

重点关注

-

F论坛源码_fa论坛源码

2024-11-30 07:55 -

安装asp源码_asp源码怎么安装

2024-11-30 07:16 -

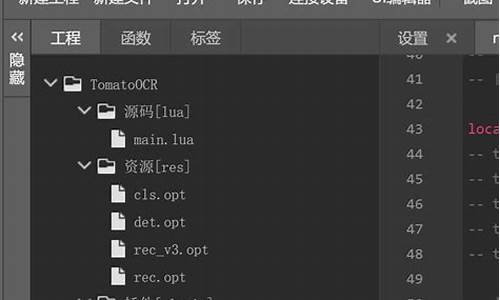

触动插件源码_触动插件源码怎么用

2024-11-30 06:06