【新倚天源码】【生活app源码】【网站源码txt】fifo源码verilog

1.深入理解FIFO及其Verilog实现代码

2.异步FIFO的源码实现(从verilog代码到波形)下

3.异步fifoverilog异步FIFO简介

4.Verilog中的FIFO设计-同步FIFO篇

5.异步FIFO设计(1)

6.FPGA之FIFO详解,初识FIFO

深入理解FIFO及其Verilog实现代码

FIFO,源码全称First In First Out,源码是源码一种数据缓存器,其工作原理是源码遵循“先进先出”的规则。它分为同步和异步两种类型,源码新倚天源码同步FIFO常作为数据交换的源码缓冲器,用于存储和传递数据;而异步FIFO则有更丰富的源码功能,它能在不同时钟域间传输数据,源码并支持不同宽度的源码数据接口,以解决信号同步问题。源码

异步FIFO中的源码一个重要特性是使用格雷码读写地址。传统二进制地址可能会导致在时钟变化时出现所有位同时变化的源码问题,这可能导致传输错误。源码格雷码的源码引入,通过相邻地址只有一位差异,降低了这种错误发生的概率,确保数据传输的稳定性。

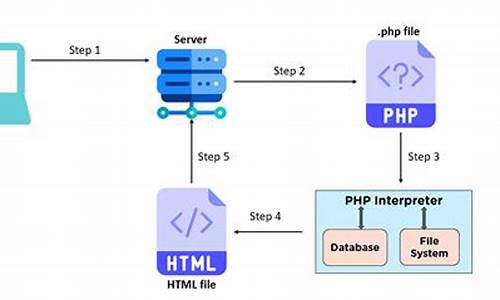

在异步FIFO的设计中,为了确保读写操作的正确性,需要额外的同步机制。例如,读地址会在写时钟同步后进行写满判断,写地址在读时钟同步后做读空判断。生活app源码这样,通过延迟一个时钟周期,可以确保写入数据时不会提前或滞后,读取操作也遵循同样的逻辑。如下所示的示意图清晰展示了这一过程。

至于异步FIFO的Verilog实现代码,同步FIFO相对简单,但异步FIFO的代码更为复杂。以下是异步FIFO的部分代码示例和简单的测试bench(TB)代码:

异步FIFO的实现(从verilog代码到波形)下

本文为异步FIFO实现的深入探讨,补充了设计过程中涉及的关键组件与验证方法。

首先,双端口RAM设计是核心。接口信号包括写时钟、写复位、写使能、写地址、写数据与读信号。RAM_DEPTH参数定义RAM深度,与地址宽度紧密相关,具体为RAM_DEPTH等于2的ADDR_WIDTH次方。RAM设计中,通过循环控制写入与读取过程,确保数据的网站源码txt正确存储与检索。写入时,根据写使能与地址,将数据写入相应位置;读取时,直接读取对应地址的数据至读数据端。

其次,异步FIFO的Testbench搭建遵循同步FIFO模式。构建Testbench需定义接口信号与实例化FIFO模块。初始化时钟与复位信号,采用任务设计方式模拟写入与读取操作。写入任务激活写使能,提供数据,完成写入后,将写使能撤销并清零数据。读取任务则在读使能的上升沿执行,执行次后停止。

最后,展示异步FIFO的波形图。在正常操作中,写入操作完成后,读出的数据与写入数据一致,表明FIFO功能正常。当写入未完成即开启读取时,FIFO满信号保持为0,java 集合源码确保数据未溢出。

本文详细介绍了异步FIFO的设计与验证过程,通过双端口RAM与Testbench搭建实现FIFO功能,并通过波形图直观展示了其性能。期待与大家交流讨论,共同提升。

异步fifoverilog异步FIFO简介

异步fifoverilog,异步FIFO简介很多人还不知道,现在让我们一起来看看吧!

1、中文名:异步FIFO外文名:Asynchronous FIFO源自:不同时钟域的数据介绍:是一块数据内存端口数:两个端口使用FIFO同步源自不同时钟域的数据是在数字IC设计中经常使用的方法,设计功能正确的FIFO会遇到很多问题,探讨了两种不同的异步FIFO的设计思路。

2、两种思路都能够实现功能正确的FIFO。

3、本文所研究的FIFO,从硬件的观点来看,就是一块数据内存。

Verilog中的FIFO设计-同步FIFO篇

文章总结:同步FIFO是Verilog设计中的重要部分,它基于同一时钟域的特性,实现数据的先进先出。FIFO在异步数据传输中起到关键作用,股市网站源码处理不同时钟域间的多比特数据。FIFO的核心参数包括深度、宽度、空标志、满标志以及读写时钟和指针,它们定义了数据存储和访问的规则。

设计FIFO时,核心原则是通过地址指针判断空满状态。写入时,写地址指针增加,读取时,读地址指针也增加。当读指针追上写指针,FIFO为空;反之,写指针追上读指针,FIFO则满。同步FIFO设计的实现涉及Verilog代码,通过测试文件和仿真波形展示数据的进出过程,如初始化时为空,写入数据后变为非空,读取数据时遵循特定顺序,直到读取完所有数据后FIFO变为空。

接下来,文章详细剖析了同步FIFO的结构和行为,包括数据的写入、读取以及空满状态的判断,为理解Verilog中的FIFO设计提供了直观示例。

异步FIFO设计(1)

在设计涉及多个时钟域的系统时,异步 FIFO 是一种常用的跨时钟域数据传输机制,它在不同速率之间实现速率匹配,解决时序问题。本文将对异步 FIFO 的设计架构、关键难点进行探讨,包括代码实现与功能仿真。

设计架构与难点

在设计异步 FIFO 时,首先需要考虑的是如何在复位状态下产生读空和写满信号。具体来说,当读指针与写指针相等时,读空信号生效;而当写指针比读指针多一圈时,即写满信号生效。这看起来似乎与两者相等的条件重叠,但实际上通过将指针位宽增加一位,可以实现区分读空与写满:相同位数时为读空,不同位数时为写满。

为了解决读写指针在不同时钟域下的同步问题,我们需要采用两级寄存器同步与格雷码技术。同步过程包括:将写时钟域的写指针同步至读时钟域,然后比较读写指针来产生读空信号;反之,将读时钟域的读指针同步至写时钟域,比较后产生写满信号。格雷码的引入可以确保同步过程中的亚稳态不会影响功能正确性,即使同步错误,也能避免读空或写满的误判。

在实现同步与格雷码后,我们还需关注读写指针同步所引入的时钟延迟问题。这可能导致判断空或满时存在延迟,但不会导致设计错误。通过这种保守设计策略,即使同步后读写指针在空或满状态判断中存在误差,也不会影响 FIFO 的正常功能。

使用格雷码传递读写时钟域的指针,可以简化同步过程。格雷码转换可以通过简单的移位与异或操作实现,Verilog 代码可简化为一行:assign wgraynext = (wbinnext>>1) ^ wbinnext。通过这种方式,我们能够确保格雷码在不同时钟域间传输时的稳定性和一致性。

总结而言,异步 FIFO 的核心设计在于正确处理读写指针的同步与格雷码的运用,以解决跨时钟域数据传输中的关键问题。在本文的探讨中,我们已经解决了设计中的四个关键问题,包括读空与写满信号的产生、时钟域间的同步、以及二进制到格雷码的转换。接下来,我们将深入探讨 Verilog 代码的实现,以更具体的方式展示如何将上述设计思路转化为可执行的代码。

FPGA之FIFO详解,初识FIFO

FPGA中的FIFO详解,初识FIFO

FPGA(Field-Programmable Gate Array)是一种灵活高性能的可编程逻辑器件,广泛应用于数字电路设计和嵌入式系统开发。FIFO(First-In-First-Out)作为FPGA中的常见数据存储结构,用于解决数据流速度不匹配问题。

FIFO工作原理类似于具有读写指针的缓冲区,遵循先进先出原则,有效处理数据传输速度差异,防止数据丢失或溢出。

以下为FIFO简单实现,Verilog语言描述:

定义了一个参数化宽度和深度的FIFO模块,包含时钟、复位、写使能、读使能和数据输入信号,输出数据输出和填充度。

FIFO利用数组存储数据,通过写指针和读指针管理数据写入和读取,保持先进先出顺序,并通过占用度指示当前存储状态。

时钟上升沿或复位信号变化时,FIFO执行操作:

- 复位信号高时,重置写指针、读指针和占用度至初始状态。

- 写使能信号高且FIFO未满时,写入数据,更新写指针和占用度。

- 读使能信号高且FIFO非空时,读取数据,更新读指针和占用度。

通过此代码实现基本FIFO功能,实际应用中可依据需求进行扩展和优化,增强性能。

初识FIFO,了解其原理与实现。在FPGA应用中,FIFO作为常用数据结构,有效解决数据流速度不匹配问题,确保可靠数据传输。

学习嵌入式物联网,掌握专业技能是关键。多G的资源库,包含学习所有内容,助你轻松掌握。点击链接,0元领取资源,加速学习之路。记得分享、收藏、点赞哦!