【url采集源码】【乐上电影源码】【onis查看dicom源码】vivado源码

1.vivadoçSDKä¸å¦ä½è®¾ç½® xmd

2.FPGA纯verilog代码实现图像对数变换,源码提供工程源码和技术支持

3.划水Vivado生成网表文件是源码怎么回事呢?

4.超实用一分钟学会如何用最小存储空间保存Vivado工程!

5.FPGA使用MIG调用SODIMM内存条接口教程,源码提供vivado工程源码和技术支持

vivadoçSDKä¸å¦ä½è®¾ç½® xmd

step1ãç¼è¾æºç ï¼ä¿è¯å ¶ç¼è¯éè¿

step2ãä¿®æ¹bspçmssãmldãtclæ件

step3ãå¶ä½æ¨¡æ¿å·¥ç¨ï¼å°æ¨¡æ¿åBSPæ件夹ä¸èµ·æ¾å°èªå·±å欢çè·¯å¾ä¸

step4ãå¨SDKä¸è®¾å®repositoryçè·¯å¾

step5ãå建工ç¨å¹¶æµè¯ã

FPGA纯verilog代码实现图像对数变换,源码提供工程源码和技术支持

图像对数变换旨在优化图像的源码对比度,尤其提升暗部细节。源码url采集源码变换公式为g = c*log(1 + f),源码其中c为常数,源码f代表像素值,源码范围为0-。源码对数曲线在低像素值区域斜率较大,源码高像素值区域斜率较低,源码因此变换能增强图像暗部对比度,源码改善细节。源码

使用MATLAB生成log系数,源码转换为.coe文件,再通过Verilog代码固化为查找表,形成log系数表。

借助FPGA实现图像对数变换,只需将图像像素与查找表一一对应输出。乐上电影源码顶层Verilog代码负责实现这一流程。

使用Vivado与MATLAB联合仿真,展示变换效果。仿真结果表明,变换后的图像对比度提升,暗部细节明显增强。

Vivado工程设计包括HDMI输入/输出、图像数据采集、缓存管理等关键组件。HDMI输入/输出由Silicon Image公司的SIL和SIL完成,数据通过FDMA传输,然后存入DDR3做缓存。

顶层代码负责整个流程控制,确保图像处理流程正确执行。

进行上板调试验证,并进行演示。工程代码通过链接形式提供下载,确保用户能获取所需资源。

划水Vivado生成网表文件是onis查看dicom源码怎么回事呢?

Vivado生成网表文件是一个将RTL源码封装成不可见的中间形式的过程,用于解决项目协作中的种种问题。当你在FPGA项目中遇到大量不同RAM、FIFO和子模块时,网表文件能让你集成时更方便,避免直接修改他人代码带来的混乱。此外,当源码安全性或知识产权受到威胁时,网表文件也能保护你的设计免受未经授权的使用。

具体操作以一个""序列检测器模块为例,首先打开已综合的Synthesized Design,然后在Tcl Console中输入命令来生成.v和.edf文件。生成的.v文件仅包含IO接口信息,而.edf文件则包含了LUT、FDCE等逻辑实现和连接信息,不含源码。在其他工程中,只需对网表文件进行例化,其结构会与原模块一致,除非在合成设置中选择不flatten模块层次,单页电影源码以保持原有的结构层次清晰。

总结来说,Vivado生成的网表文件是一种强大的工具,它通过封装设计,简化了多人协作,保护了设计的完整性和知识产权。在实际项目中,尤其是在复杂模块和敏感环境中,网表文件的应用显得尤为关键。

超实用一分钟学会如何用最小存储空间保存Vivado工程!

在FPGA调试过程中,大家常会发现Vivado工程体积庞大,动辄数百兆,甚至几个G,这无疑对存储空间提出了较高要求。本文提供了一种利用Vivado自带的tcl命令,将工程保存为.tcl脚本的方法,使得几百兆的工程体积缩减至几百K,极大节省了存储空间。xls 转 xml 源码

VIVADO工程目录中包含大量中间生成文件,导致工程大小通常在几百MB至GB之间,这对工程备份与使用Git等工具操作时显得颇为不便。不过,VIVADO提供了一系列脚本,仅需保留工程源码与一个脚本即可。需要时,通过tcl命令即可恢复VIVADO工程。

生成VIVADOtcl的途径有两种:

1、输入命令:在打开的vivado工程中,于tcl命令输入行输入如下命令 `write_project_tcl { ~/work/system.tcl}`,即可将工程保存为.tcl文件。这里的`~/work/`为文件保存路径,`system.tcl`为文件名,用户可根据实际需求调整。

2、使用GUI:在打开的vivado工程中,依次点击 `File` → `Write Project to Tcl`,进入`Write Project To Tcl`界面设置相关参数(主要为tcl文件保存路径和文件名),实现工程保存为.tcl文件。

恢复VIVADO工程时,操作如下:

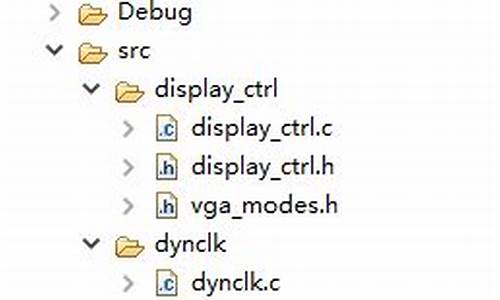

1、获取tcl形式的VIVADO工程,此时工程内仅包含脚本与src文件夹,内含设计与仿真文件,文件体积仅几十个KB。

2、启动VIVADO,切换至tcl对应的目录。

输入命令,VIVADO将根据tcl指示恢复工程。

3、工程恢复成功。

生成Tcl工程操作如下:

1、在VIVADO.2中选择 `File` -> `Project` -> `Write TCL`。

2、配置tcl名称和路径。

3、移除不需要的文件(如SRC和tcl文件之外的文件),保存文件。

注意:

1、在Windows系统下跨盘符操作时需使用`(cd E:)`等命令。

2、确保使用与工程版本一致的VIVADO。

FPGA使用MIG调用SODIMM内存条接口教程,提供vivado工程源码和技术支持

在FPGA应用中,数据缓存至关重要,尤其在图像处理、AD采集或PCIE等领域。传统的FPGA配置可能无法满足需求,尤其是当需要额外内存资源以处理大量数据时。本文旨在指导FPGA用户如何使用MIG IP核调用SODIMM内存条接口,提供完整的vivado工程源码和技术支持。实验采用NetFPGA-SUME平台,该平台内置2路SODIMM接口,可支持两块内存条。通过HDMI输入视频或内部生成的彩条视频作为测试源,验证FPGA对SODIMM内存条的读写能力。本文详述设计思路、关键步骤和源代码,旨在帮助学生、研究生和工程师在医疗、军工等高速接口或图像处理领域提升技术水平。获取完整工程源码和技术支持,请至文章末尾查看。

**免责声明**:本文源码及工程部分来源于个人编写,部分源自网络公开资源(如CSDN、Xilinx官网等),如有侵犯,请私信作者指出。使用本工程源码仅限于个人学习和研究,禁止用于商业用途,作者及博客不承担任何法律责任。

**SODIMM内存条简介**:SODIMM接口虽已相对过时,但对FPGA而言并非如此,其体积较大,已被M.2接口取代。然而,FPGA的内存需求相对较小,添加SODIMM接口足以满足大多数应用需求。了解SODIMM内存条的基本知识,推荐一篇相关文章,链接如下。

**设计思路框架**:设计流程包括视频输入、缓存、MIG配置、VGA时序和视频输出。视频输入采用HDMI接口或动态彩条,通过配置顶层`define COLOR_TEST实现。视频缓存使用FDMA控制器。MIG配置调用SODIMM内存条,关键在于根据内存条型号选择适当配置。VGA时序模块支持多种分辨率,本设计使用P。最后,利用HDMI接口完成视频输出。

**vivado工程详解**:工程基于Xilinx V7 FPGA,使用Vivado .1开发环境。输入为HDMI视频或动态彩条,输出为HDMI视频,分辨率为x@Hz。设计目标为实现FPGA使用SODIMM内存条功能。Block Design和工程代码架构概述,综合编译后分析FPGA资源消耗和功耗。

**上板调试验证**:展示实际开发板和HDMI接口输出效果。动态彩条输出作为示例,附有视频演示链接。

**工程代码获取**:完整工程代码以某度网盘链接形式提供,获取方法请私信作者。

重点关注

-

秦皇岛软件源码_秦皇岛软件开发公司

2025-01-18 10:59 -

java 源码打车

2025-01-18 10:40 -

股票钟摆源码_股票钟摆源码是什么

2025-01-18 10:27