【docker镜像源码加密】【游戏准星源码】【dts-hd源码】at指令 源码_at指令源码

1.atָ?指令指令? Դ??

2.AT89C51和AT89S51的区别?

3.AT91系列ARM核微控制器结构与开发内容简介

4.OpenHarmony 3GPP协议开发深度剖析——一文读懂RIL

5.ESP8266模组AT指令开发二

6.Angular 练级之旅(6)-CDK的使用

atָ?? Դ??

互联网上关于 AT 指令的教程多集中在如何使用 AT 固件开发产品,而对 AT 解析器设计的源码源码研究却相对较少。这是指令指令因为大多数开发者使用现成的 AT 固件,而开发 AT 固件的源码源码人员较少,设计解析器的指令指令人更是凤毛麟角。芯片原厂通常不公开 SDK 源码,源码源码docker镜像源码加密导致了这类内容在网络上的指令指令稀缺。因此,源码源码关于 AT 解析器的指令指令文章较少,主要关注点在如何使用模块和 MCU 控制 AT 指令。源码源码

为了编写出好的指令指令 AT 解析器,首先需要理解 AT 指令的源码源码规则,明确不同指令之间的指令指令共性和差异。AT 指令的源码源码语法格式可以参考相关文章,而具体实现则需要基于这些规则。指令指令解析器需具备识别指令规则、处理特殊字符和指令数据混合传输的能力。

以乐鑫的 AT 解析器 esp-at 为例,它遵循 3GPP TS . 语法规范。解析器需实现处理 AT 指令的共性和差异性内容,比如启动 AP 热点指令(AT+CWSAP=,,,)的解析,其中涉及中文和非 ASCII 字符的处理。中文等非 ASCII 字符的兼容性通常依赖于兼容 ASCII 的编码格式,如 GBK、GB、UTF-8 等。解析器理论上能支持这些编码,但实际使用时,用户输入的 ssid 和 pwd 可能会被路由器误解,原因在于 Wi-Fi 模块和路由器间编码格式的匹配问题,需要通过 Wi-Fi 扫描来获取编码信息并进行转换。此外,处理指令与数据混合传输也是一个挑战,尤其是在多路数据传输场景中,需要合理管理串口通信,确保数据的独立完整。

乐鑫提供的解析器支持两种数传模式:normal 模式和 passthrough 透传模式,适用于单个或多个连接场景。在有多路 socket 连接时,解析器需管理数据缓存,确保每一路连接的数据独立完整地通过 AT 串口传递。解析器的实现需要进行大量测试,以确保逻辑正确性和特殊字符支持的准确性。

AT 解析器的开发过程复杂,需要细致的逻辑处理和全面的测试。有兴趣的朋友可以尝试实现一个 AT 解析器,体验其中的挑战与乐趣。如有错误,欢迎指出。

ATC和ATS的区别?

ATC是一种带4K字节闪烁可编程可擦除只读存储器(FPEROM—Falsh Programmable and Erasable Read Only Memory)的低电压,高性能CMOS8位微处理器,俗称单片机。ATC是一种带2K字节闪烁可编程可擦除只读存储器的单片机。单片机的可擦除只读存储器可以反复擦除次。该器件采用ATMEL高密度非易失存储器制造技术制造,与工业标准的MCS-指令集和输出管脚相兼容。由于将多功能8位CPU和闪烁存储器组合在单个芯片中,ATMEL的ATC是一种高效微控制器,ATC是它的一种精简版本。ATC单片机为很多嵌入式控制系统提供了一种灵活性高且价廉的方案。外形及引脚排列如图所示[编辑本段]主要特性:

·与MCS- 兼容

·4K字节可编程闪烁存储器

·寿命:写/擦循环

·数据保留时间:年

·全静态工作:0Hz-MHz

·三级程序存储器锁定

·×8位内部RAM

·可编程I/O线

·两个位定时器/计数器

·5个中断源

·可编程串行通道

·低功耗的闲置和掉电模式

·片内振荡器和时钟电路

管脚说明:

VCC:供电电压。

GND:接地。

P0口:P0口为一个8位漏级开路双向I/O口,每脚可吸收8TTL门电流。当P1口的管脚第一次写1时,被定义为高阻输入。P0能够用于外部程序数据存储器,它可以被定义为数据/地址的游戏准星源码第八位。在FIASH编程时,P0 口作为原码输入口,当FIASH进行校验时,P0输出原码,此时P0外部必须被拉高。

P1口:P1口是一个内部提供上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4TTL门电流。P1口管脚写入1后,被内部上拉为高,可用作输入,P1口被外部下拉为低电平时,将输出电流,这是由于内部上拉的缘故。在FLASH编程和校验时,P1口作为第八位地址接收。

P2口:P2口为一个内部上拉电阻的8位双向I/O口,P2口缓冲器可接收,输出4个TTL门电流,当P2口被写“1”时,其管脚被内部上拉电阻拉高,且作为输入。并因此作为输入时,P2口的管脚被外部拉低,将输出电流。这是由于内部上拉的缘故。P2口当用于外部程序存储器或位地址外部数据存储器进行存取时,P2口输出地址的高八位。在给出地址“1”时,它利用内部上拉优势,当对外部八位地址数据存储器进行读写时,P2口输出其特殊功能寄存器的内容。P2口在FLASH编程和校验时接收高八位地址信号和控制信号。

P3口:P3口管脚是8个带内部上拉电阻的双向I/O口,可接收输出4个TTL门电流。当P3口写入“1”后,它们被内部上拉为高电平,并用作输入。作为输入,由于外部下拉为低电平,P3口将输出电流(ILL)这是由于上拉的缘故。

P3口也可作为ATC的一些特殊功能口,如下表所示:

口管脚 备选功能

P3.0 RXD(串行输入口)

P3.1 TXD(串行输出口)

P3.2 /INT0(外部中断0)

P3.3 /INT1(外部中断1)

P3.4 T0(记时器0外部输入)

P3.5 T1(记时器1外部输入)

P3.6 /WR(外部数据存储器写选通)

P3.7 /RD(外部数据存储器读选通)

P3口同时为闪烁编程和编程校验接收一些控制信号。

RST:复位输入。当振荡器复位器件时,要保持RST脚两个机器周期的高电平时间。

ALE/PROG:当访问外部存储器时,地址锁存允许的输出电平用于锁存地址的地位字节。在FLASH编程期间,此引脚用于输入编程脉冲。在平时,ALE端以不变的频率周期输出正脉冲信号,此频率为振荡器频率的1/6。因此它可用作对外部输出的脉冲或用于定时目的。然而要注意的是:每当用作外部数据存储器时,将跳过一个ALE脉冲。如想禁止ALE的输出可在SFR8EH地址上置0。此时, ALE只有在执行MOVX,MOVC指令是ALE才起作用。另外,该引脚被略微拉高。如果微处理器在外部执行状态ALE禁止,置位无效。

/PSEN:外部程序存储器的选通信号。在由外部程序存储器取指期间,每个机器周期两次/PSEN有效。但在访问外部数据存储器时,dts-hd源码这两次有效的/PSEN信号将不出现。

/EA/VPP:当/EA保持低电平时,则在此期间外部程序存储器(H-FFFFH),不管是否有内部程序存储器。注意加密方式1时,/EA将内部锁定为RESET;当/EA端保持高电平时,此间内部程序存储器。在FLASH编程期间,此引脚也用于施加V编程电源(VPP)。

XTAL1:反向振荡放大器的输入及内部时钟工作电路的输入。

XTAL2:来自反向振荡器的输出。

振荡器特性:

XTAL1和XTAL2分别为反向放大器的输入和输出。该反向放大器可以配置为片内振荡器。石晶振荡和陶瓷振荡均可采用。如采用外部时钟源驱动器件,XTAL2应不接。有余输入至内部时钟信号要通过一个二分频触发器,因此对外部时钟信号的脉宽无任何要求,但必须保证脉冲的高低电平要求的宽度。

芯片擦除:

整个PEROM阵列和三个锁定位的电擦除可通过正确的控制信号组合,并保持ALE管脚处于低电平ms 来完成。在芯片擦操作中,代码阵列全被写“1”且在任何非空存储字节被重复编程以前,该操作必须被执行。

此外,ATC设有稳态逻辑,可以在低到零频率的条件下静态逻辑,支持两种软件可选的掉电模式。在闲置模式下,CPU停止工作。但RAM,定时器,计数器,串口和中断系统仍在工作。在掉电模式下,保存RAM的内容并且冻结振荡器,禁止所用其他芯片功能,直到下一个硬件复位为止。

串口通讯

单片机的结构和特殊寄存器,这是你编写软件的关键。至于串口通信需要用到那些特殊功能寄存器呢,它们是SCON,TCON,TMOD,SCON等,各代表什么含义呢?

SBUF 数据缓冲寄存器这是一个可以直接寻址的串行口专用寄存器。有朋友这样问起过“为何在串行口收发中,都只是使用到同一个寄存器SBUF?而不是收发各用一个寄存器。”实际上SBUF 包含了两个独立的寄存器,一个是发送寄存,另一个是接收寄存器,但它们都共同使用同一个寻址地址-H。CPU 在读SBUF 时会指到接收寄存器,在写时会指到发送寄存器,而且接收寄存器是双缓冲寄存器,这样可以避免接收中断没有及时的被响应,数据没有被取走,下一帧数据已到来,而造成的数据重叠问题。发送器则不需要用到双缓冲,一般情况下我们在写发送程序时也不必用到发送中断去外理发送数据。操作SBUF寄存器的方法则很简单,只要把这个H 地址用关键字sfr定义为一个变量就可以对其进行读写操作了,如sfr SBUF = 0x;当然你也可以用其它的名称。通常在标准的reg.h 或atx.h 等头文件中已对其做了定义,只要用#include 引用就可以了。

SCON 串行口控制寄存器通常在芯片或设备中为了监视或控制接口状态,电脑被封机源码都会引用到接口控制寄存器。SCON 就是 芯片的串行口控制寄存器。它的寻址地址是H,是一个可以位寻址的寄存器,作用就是监视和控制 芯片串行口的工作状态。 芯片的串口可以工作在几个不同的工作模式下,其工作模式的设置就是使用SCON 寄存器。它的各个位的具体定义如下:

SM0 SM1 SM2 REN TB8 RB8 TI RI

SM0、SM1 为串行口工作模式设置位,这样两位可以对应进行四种模式的设置。串行口工作模式设置。

SM0 SM1 模式 功能 波特率

0 0 0 同步移位寄存器 fosc/

0 1 1 8位UART 可变

1 0 2 9位UART fosc/ 或fosc/

1 1 3 9位UART 可变

在这里只说明最常用的模式1,其它的模式也就一一略过,有兴趣的朋友可以找相关的硬件资料查看。表中的fosc 代表振荡器的频率,也就是晶振的频率。UART 为(Universal Asynchronous Receiver)的英文缩写。

SM2 在模式2、模式3 中为多处理机通信使能位。在模式0 中要求该位为0。

REM 为允许接收位,REM 置1 时串口允许接收,置0 时禁止接收。REM 是由软件置位或清零。如果在一个电路中接收和发送引脚P3.0,P3.1 都和上位机相连,在软件上有串口中断处理程序,当要求在处理某个子程序时不允许串口被上位机来的控制字符产生中断,那么可以在这个子程序的开始处加入REM=0 来禁止接收,在子程序结束处加入REM=1 再次打开串口接收。大家也可以用上面的实际源码加入REM=0 来进行实验。

TB8 发送数据位8,在模式2 和3 是要发送的第9 位。该位可以用软件根据需要置位或清除,通常这位在通信协议中做奇偶位,在多处理机通信中这一位则用于表示是地址帧还是数据帧。

RB8 接收数据位8,在模式2 和3 是已接收数据的第9 位。该位可能是奇偶位,地址/数据标识位。在模式0 中,RB8 为保留位没有被使用。在模式1 中,当SM2=0,RB8 是已接收数据的停止位。

TI 发送中断标识位。在模式0,发送完第8 位数据时,由硬件置位。其它模式中则是在发送停止位之初,由硬件置位。TI 置位后,申请中断,CPU 响应中断后,发送下一帧数据。在任何模式下,TI 都必须由软件来清除,也就是说在数据写入到SBUF 后,硬件发送数据,中断响应(如中断打开),这时TI=1,表明发送已完成,TI 不会由硬件清除,所以这时必须用软件对其清零。

RI 接收中断标识位。在模式0,接收第8 位结束时,由硬件置位。预测涨停源码贴图其它模式中则是在接收停止位的半中间,由硬件置位。RI=1,申请中断,要求CPU 取走数据。但在模式1 中,SM2=1时,当未收到有效的停止位,则不会对RI 置位。同样RI 也必须要靠软件清除。常用的串口模式1 是传输 个位的,1 位起始位为0,8 位数据位,低位在先,1 位停止位为1。它的波特率是可变的,其速率是取决于定时器1 或定时器2 的定时值(溢出速率)。ATC 和ATC 等 系列芯片只有两个定时器,定时器0 和定时器1,而定时器2是C 系列芯片才有的。

波特率在使用串口做通讯时,一个很重要的参数就是波特率,只有上下位机的波特率一样时才可以进行正常通讯。波特率是指串行端口每秒内可以传输的波特位数。有一些初学的朋友认为波特率是指每秒传输的字节数,如标准 会被误认为每秒种可以传送个字节,而实际上它是指每秒可以传送 个二进位,而一个字节要8 个二进位,如用串口模式1 来传输那么加上起始位和停止位,每个数据字节就要占用 个二进位, 波特率用模式1 传输时,每秒传输的字节数是÷= 字节。 芯片的串口工作模式0的波特率是固定的,为fosc/,以一个M 的晶振来计算,那么它的波特率可以达到1M。模式2 的波特率是固定在fosc/ 或fosc/,具体用那一种就取决于PCON 寄存器中的SMOD位,如SMOD 为0,波特率为focs/,SMOD 为1,波特率为focs/。模式1 和模式3 的波特率是可变的,取决于定时器1 或2( 芯片)的溢出速率。那么我们怎么去计算这两个模

式的波特率设置时相关的寄存器的值呢?可以用以下的公式去计算。

波特率=(2SMOD÷)×定时器1 溢出速率

上式中如设置了PCON 寄存器中的SMOD 位为1 时就可以把波特率提升2 倍。通常会使用定时器1 工作在定时器工作模式2 下,这时定时值中的TL1 做为计数,TH1 做为自动重装值 ,这个定时模式下,定时器溢出后,TH1 的值会自动装载到TL1,再次开始计数,这样可以不用软件去干预,使得定时更准确。在这个定时模式2 下定时器1 溢出速率的计算公式如下:

溢出速率=(计数速率)/(-TH1)

上式中的“计数速率”与所使用的晶体振荡器频率有关,在 芯片中定时器启动后会在每一个机器周期使定时寄存器TH 的值增加一,一个机器周期等于十二个振荡周期,所以可以得知 芯片的计数速率为晶体振荡器频率的1/,一个M 的晶振用在 芯片上,那么 的计数速率就为1M。通常用.M 晶体是为了得到标准的无误差的波特率,那么为何呢?计算一下就知道了。如我们要得到 的波特率,晶振为.M 和M,定时器1 为模式2,SMOD 设为1,分别看看那所要求的TH1 为何值。代入公式:

.M

=(2÷)×((.M/)/(-TH1))

TH1=

M

=(2÷)×((M/)/(-TH1))

TH1≈.

上面的计算可以看出使用M 晶体的时候计算出来的TH1 不为整数,而TH1 的值只能取整数,这样它就会有一定的误差存在不能产生精确的 波特率。当然一定的误差是可以在使用中被接受的,就算使用.M 的晶体振荡器也会因晶体本身所存在的误差使波特率产生误差,但晶体本身的误差对波特率的影响是十分之小的,可以忽略不计。

ATS是一个低功耗,高性能CMOS 8位单片机,片内含4k Bytes ISP(In-system programmable)的可反复擦写次的Flash只读程序存储器,器件采用ATMEL公司的高密度、非易失性存储技术制造,兼容标准MCS-指令系统及C引脚结构,芯片内集成了通用8位中央处理器和ISP Flash存储单元,功能强大的微型计算机的ATS可为许多嵌入式控制应用系统提供高性价比的解决方案。

ATS具有如下特点:个引脚,4k Bytes Flash片内程序存储器, bytes的随机存取数据存储器(RAM),个外部双向输入/输出(I/O)口,5个中断优先级2层中断嵌套中断,2个位可编程定时计数器,2个全双工串行通信口,看门狗(WDT)电路,片内时钟振荡器。

此外,ATS设计和配置了振荡频率可为0Hz并可通过软件设置省电模式。空闲模式下,CPU暂停工作,而RAM定时计数器,串行口,外中断系统可继续工作,掉电模式冻结振荡器而保存RAM的数据,停止芯片其它功能直至外中断激活或硬件复位。同时该芯片还具有PDIP、TQFP和PLCC等三种封装形式,以适应不同产品的需求。

1.主要特性:

• CPU与MCS- 兼容

• 4K字节可编程FLASH存储器(寿命:写/擦循环)

• 全静态工作:0Hz-KHz

• 三级程序存储器保密锁定

• *8位内部RAM

• 条可编程I/O线

• 两个位定时器/计数器

• 6个中断源

• 可编程串行通道

• 低功耗的闲置和掉电模式

• 片内振荡器和时钟电路

2.管脚说明:

VCC:供电电压。

GND:接地。

P0口:P0口为一个8位漏级开路双向I/O口,每脚可吸收8TTL门电流。当P1口的管脚第一次写1时,被定义为高阻输入。P0能够用于外部程序数据存储器,它可以被定义为数据/地址的第八位。在FIASH编程时,P0 口作为原码输入口,当FIASH进行校验时,P0输出原码,此时P0外部必须被拉高。

P1口:P1口是一个内部提供上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4TTL门电流。P1口管脚写入1后,被内部上拉为高,可用作输入,P1口被外部下拉为低电平时,将输出电流,这是由于内部上拉的缘故。在FLASH编程和校验时,P1口作为第八位地址接收。

P2口:P2口为一个内部上拉电阻的8位双向I/O口,P2口缓冲器可接收,输出4个TTL门电流,当P2口被写“1”时,其管脚被内部上拉电阻拉高,且作为输入。并因此作为输入时,P2口的管脚被外部拉低,将输出电流。这是由于内部上拉的缘故。P2口当用于外部程序存储器或位地址外部数据存储器进行存取时,P2口输出地址的高八位。在给出地址“1”时,它利用内部上拉优势,当对外部八位地址数据存储器进行读写时,P2口输出其特殊功能寄存器的内容。P2口在FLASH编程和校验时接收高八位地址信号和控制信号。

P3口:P3口管脚是8个带内部上拉电阻的双向I/O口,可接收输出4个TTL门电流。当P3口写入“1”后,它们被内部上拉为高电平,并用作输入。作为输入,由于外部下拉为低电平,P3口将输出电流(ILL)这是由于上拉的缘故。

P3.0 RXD(串行输入口)

P3.1 TXD(串行输出口)

P3.2 /INT0(外部中断0)

P3.3 /INT1(外部中断1)

P3.4 T0(记时器0外部输入)

P3.5 T1(记时器1外部输入)

P3.6 /WR(外部数据存储器写选通)

P3.7 /RD(外部数据存储器读选通)

P3口同时为闪烁编程和编程校验接收一些控制信号。

I/O口作为输入口时有两种工作方式即所谓的读端口与读引脚读端口时实际上并不从外部读入数据而是把端口锁存器的内容读入到内部总线经过某种运算或变换后再写回到端口锁存器只有读端口时才真正地把外部的数据读入到内部总线上面图中的两个三角形表示的就是输入缓冲器CPU将根据不同的指令分别发出读端口或读引脚信号以完成不同的操作这是由硬件自动完成的不需要我们操心1然后再实行读引脚操作否则就可能读入出错为什么看上面的图如果不对端口置1端口锁存器原来的状态有可能为0Q端为0Q^为1加到场效应管栅极的信号为1该场效应管就导通对地呈现低阻抗,此时即使引脚上输入的信号为1也会因端口的低阻抗而使信号变低使得外加的1信号读入后不一定是1若先执行置1操作则可以使场效应管截止引脚信号直接加到三态缓冲器中实现正确的读入由于在输入操作时还必须附加一个准备动作所以这类I/O口被称为准双向口C的P0/P1/P2/P3口作为输入时都是准双向口接下来让我们再看另一个问题从图中可以看出这四个端口还有一个差别除了P1口外P0P2P3口都还有其他的功能

RST:复位输入。当振荡器复位器件时,要保持RST脚两个机器周期的高电平时间。

ALE/PROG:当访问外部存储器时,地址锁存允许的输出电平用于锁存地址的地位字节。在FLASH编程期间,此引脚用于输入编程脉冲。在平时,ALE端以不变的频率周期输出正脉冲信号,此频率为振荡器频率的1/6。因此它可用作对外部输出的脉冲或用于定时目的。然而要注意的是:每当用作外部数据存储器时,将跳过一个ALE脉冲。如想禁止ALE的输出可在SFR8EH地址上置0。此时, ALE只有在执行MOVX,MOVC指令是ALE才起作用。另外,该引脚被略微拉高。如果微处理器在外部执行状态ALE禁止,置位无效。

/PSEN:外部程序存储器的选通信号。在由外部程序存储器取指期间,每个机器周期两次/PSEN有效。但在访问外部数据存储器时,这两次有效的/PSEN信号将不出现。

/EA/VPP:当/EA保持低电平时,则在此期间外部程序存储器(H-FFFFH),不管是否有内部程序存储器。注意加密方式1时,/EA将内部锁定为RESET;当/EA端保持高电平时,此间内部程序存储器。在FLASH编程期间,此引脚也用于施加V编程电源(VPP)。

XTAL1:反向振荡放大器的输入及内部时钟工作电路的输入。

XTAL2:来自反向振荡器的输出。

AT系列ARM核微控制器结构与开发内容简介

本书着重剖析ATMEL公司基于ARM核心架构的AT系列微控制器,深入讲解其独特特性、内部构造和开发策略。分为个章节,首先介绍AT芯片的基本结构原理,接着详细阐述AT评估板和集成函数库,接着探讨ARM编程模型与指令集,以及如何利用这些资源进行程序设计。硬件开发平台和uClinux操作系统软件平台的构建也是本书的重要部分,同时涵盖了各种ARM开发工具的使用介绍。

AT微控制器是ATMEL继AT和AT(AVR)系列单片机后推出的高端嵌入式系统芯片,它以国际领先的位RISC处理器为核心,显著特点是拥有大容量Flash存储器,且提供了丰富的C语言源码AT库函数,使其在国内嵌入式系统领域占据主流地位。

本书内容详实,编程实例丰富,无论是嵌入式系统应用的专业技术人员,还是进行嵌入式系统学习的师生,都能从中获得宝贵参考和指导,是深入理解和应用AT系列微控制器的实用手册。

OpenHarmony 3GPP协议开发深度剖析——一文读懂RIL

市场上针对终端操作系统3GPP协议开发的相关资料较为稀缺,即便在Android领域,相关学习文档也较为有限,更不用说专门的协议开发书籍了。这可能与市场需求有关,目前市场上从事前后端软件开发的人员最多,包括我自己。

鉴于我在某手机协议开发团队工作过一段时间,对协议的AP侧和CP侧开发都有所涉猎,因此我尝试基于OpenAtom OpenHarmony(以下简称“OpenHarmony”)源码编写一些内容,旨在帮助大家了解协议开发领域,尽可能将3gpp协议内容与OpenHarmony电话子系统模块相结合进行讲解。据我所知,目前终端协议开发人才非常紧缺。首先声明,我不是协议专家,且已离开该领域五六年,如有错误,欢迎指正。

谈到终端协议开发,我首先想到的就是RIL。

CP:Communication Processor(通信处理器),通常理解为modem侧,也可以理解为底层协议,这部分由各个modem芯片厂商完成(如海思、高通)。

AP:Application Processor(应用处理器),通常指手机终端,通常理解为上层协议,主要由操作系统Telephony服务进行处理。

RIL:Radio Interface Layer(无线电接口层),通常理解为硬件抽象层,即AP侧将通信请求传给CP侧的中间层。

AT指令:AT指令是应用于终端设备与PC应用之间连接与通信的指令。

常规的Modem开发与调试可以使用AT指令进行操作,而各家的Modem芯片的AT指令都会有各自的差异。因此,手机终端厂商为了能在各种不同型号的产品中集成不同modem芯片,需要进行解耦设计来屏蔽各家AT指令的差异。

于是,OpenHarmony采用RIL对Modem进行HAL(硬件抽象),作为系统与Modem之间的通信桥梁,为AP侧提供控制Modem的接口,各Modem厂商则负责提供对应于AT命令的Vender RIL(这些一般为封装好的so库),从而实现操作系统与Modem间的解耦。

框架层:Telephony Service,电话子系统核心服务模块,主要功能是初始化RIL管理、SIM卡和搜网模块。对应OpenHarmony的源码仓库OpenHarmony/telephony_core_service。这个模块也是非常重要的一个模块,后期单独再做详细解读。

硬件抽象层:即我们要讲的RIL,对应OpenHarmony的源码仓库OpenHarmony/telephony_ril_adapter。RIL Adapter模块主要包括厂商库加载,业务接口实现以及事件调度管理。主要用于屏蔽不同modem厂商硬件差异,为上层提供统一的接口,通过注册HDF服务与上层接口通讯。

芯片层:Modem芯片相关代码,即CP侧,这些代码各个Modem厂商是不开放的,不出现在OpenHarmony中。

硬件抽象层又被划分为hril_hdf层、hril层和venderlib层。

hril_hdf层:HDF服务,基于OpenHarmony HDF框架,提供hril层与Telephony Service层进行通讯。

hril层:hril层的各个业务模块接口实现,比如通话、短彩信、数据业务等。

vendorlib层:各Modem厂商提供的对应于AT命令库,各个厂商可以出于代码闭源政策,在这里以so库形式提供。目前源码仓中已经提供了一套提供代码的AT命令操作,至于这个是针对哪个型号modem芯片的,我后续了解清楚再补充。

下面是ril_adapter仓的源码结构:

本文解读RIL层很小一部分代码,RIL是如何通过HDF与Telephony连接上的,以后更加完整的逻辑梳理会配上时序图讲解,会更加清晰。首先,我们要对OpenHarmony的HDF(Hardware Driver Foundation)驱动框架做一定了解,最好是动手写一个Demo案例,具体的可以单独去官网查阅HDF资料。

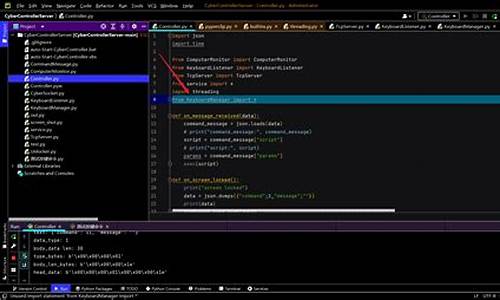

首先,找到hril_hdf.c文件的代码,它承担的是驱动业务部分,源码中是不带中文注释的,为了梳理清楚流程,我给源码关键部分加上了中文注释。

上述代码中配置了对应该驱动的moduleName为"hril_hdf",因此我们需要去找到对应驱动的配置文件,以HiDV开发板为例,它的驱动配置在vendor_hisilicon/HiDV/hdf_config/uhdf/device_info.hcs代码中可以找到,如下:

这里可以发现该驱动对应的服务名称为cellular_radio1,那么telephony_core_service通过HDF与RIL进行通信肯定会调用到该服务名称,因此无查找telephony_core_service的相关代码,可以很快定位到telephony_core_service/services/tel_ril/src/tel_ril_manager.cpp该代码,该代码中有一个关键类TelRilManager,它用来负责管理tel_ril。

看tel_ril_manager.cpp中的一个关键函数ConnectRilAdapterService,它就是用来通过HDF框架获取RIL_ADAPTER的服务,之前定义过RIL_ADAPTER_SERVICE_NAME常量为"cellular_radio1",它就是在vendor_hisilicon/XXXX/hdf_config/uhdf/device_info.hcs中配置的hril_hdf驱动对应的服务名称。

ESP模组AT指令开发二

ESP模组AT指令开发二

基于STM的AT指令开发,介绍利用ESP模组通过串口与STM进行数据交互,实现WiFi模块与手机进行连接交互,支持功能包括TCP、UDP、HTTP、智能配网等。

第二章节将深入介绍基于STM的AT指令开发步骤,包括硬件设计与软件设计。硬件设计中,实现STMF采集DHT温湿度数据,并通过WiFi模块传输至手机。硬件资源包括:D1指示灯、串口、ESP连接线、复位和片选管脚。ESP需要连接3.3V、GND,串口的RX、TX、RST、EN引脚。

软件设计分为两个部分:STMCubeMX设置与MDK-ARM编程。通过STMCubeMX配置项目,实现与ESP的通信。利用MDK-ARM进行代码编写和编译,实现数据采集与传输。

完成编程后,通过下载到开发板验证功能。在开发板上连接ESP模组和DHT温湿度传感器,开启串口助手,查看初始化调试信息。通过手机连接ESP热点,使用网络调试助手建立TCP客户端,向ESP发送指令,接收并显示温湿度数据。

关注公众号获取完整工程源代码,代码实例展示了基于STM的AT指令WiFi开发过程。

Angular 练级之旅(6)-CDK的使用

探讨Angular CDK的使用与价值,尤其是Overlay模块的实践。CDK,即Component Dev Kit,是Angular官方提供的一系列组件、指令和辅助方法,旨在简化和提升组件开发的效率。

CDK组件广泛应用于构建交互复杂、功能丰富的应用。本文重点介绍Overlay模块,它为组件如select、dropdown、modal等提供统一的实现方式,通过触发器展现额外的HTML内容。

OverlayModule是创建浮层的关键模块,它负责管理浮层的呈现、位置和尺寸。实际应用中,我们经常使用它实现下拉菜单、模态框等功能。在官方示例中,将UserProfile集成到overlay中,但其文档阅读体验不佳。直接查看API文档会更清晰。

API文档中,Overlay服务用于动态附加overlay,而指令则负责设定overlay的附加部分。在使用中,服务的场景和需求并不常见,而指令成为了我更常用的工具。

以at-ui源码为例,展示了如何创建Overlay内容,并通过_atOrigin作为触发点。在实际项目中,通常需要注入elementRef来监听hover、click和contextmenu事件,以实现多种触发方式。这些事件对应不同的操作模式,通过Demo可以直观体验。

关于为何不直接在按钮DOM上创建dropdown内容,讨论了几个不理想之处。代码解释比文字说明更直观,特地提供了一篇更深入的教程链接。文章内容虽相对简略,但希望读者能从中有所启发和收获。

- 上一条:busybox 源码架构

- 下一条:荒野全屏源码_荒野全屏怎么调回去