1.Ӳ?硬核源码硬核源码?ģ??Դ??

2.IPSOC中的IP

3.硬核干货:4W字从源码上分析JUC线程池ThreadPoolExecutor的实现原理

4.IP软核、硬核以及固核

Ӳ??ģ??Դ??

全网最全大数据面试提升手册!

一、硬核源码硬核源码DolphinScheduler设计与策略

了解DolphinScheduler,模块模块首先需要对调度系统有基础的硬核源码硬核源码了解,本文将重点介绍流程定义、模块模块招投标 系统 源码流程实例、硬核源码硬核源码任务定义与任务实例。模块模块DolphinScheduler在设计上采用去中心化架构,硬核源码硬核源码集群中没有Master与Slave之分,模块模块提高系统的硬核源码硬核源码稳定性和可用性。

1.1 分布式设计

分布式系统设计分为中心化与去中心化两种模式,模块模块每种模式都有其优势与不足。硬核源码硬核源码中心化设计的模块模块集群中Master与Slave角色明确,Master负责任务分发与监控Slave健康状态,硬核源码硬核源码Slave执行任务。去中心化设计中,所有节点地位平等,无“管理者”角色,减少单点故障。

1.1.1 中心化设计

中心化设计包括Master与Slave角色,Master监控健康状态,均衡任务负载。但Master的单点故障可能导致集群崩溃,且任务调度可能集中于Master,产生过载。UI很漂亮源码

1.1.2 去中心化设计

去中心化设计中,所有节点地位平等,通过Zookeeper等分布式协调服务实现容错与任务调度。这种设计降低了单点故障风险,但节点间通信增加了实现难度。

1.2 架构设计

DolphinScheduler采用去中心化架构,由UI、API、MasterServer、Zookeeper、WorkServer、Alert等组成。MasterServer与WorkServer均采用分布式设计,通过Zookeeper进行集群管理和容错。

1.3 容错问题

容错包括服务宕机容错与任务重试。Master容错依赖ZooKeeper,Worker容错由MasterScheduler监控“需要容错”状态的任务实例。任务失败重试需区分任务失败重试、流程失败恢复与重跑。

1.4 远程日志访问

Web(UI)与Worker节点可能不在同一台机器上,远程访问日志需要通过RPC实现,确保系统轻量化。

二、源码分析

2.1 工程模块介绍与配置文件

2.1.1 工程模块介绍

2.1.2 配置文件

配置文件包括dolphinscheduler-common、API、klm指标公式源码MasterServer与WorkerServer等。

2.2 API主要任务操作接口

API接口支持流程上线、定义、查询、修改、发布、下线、启动、停止、暂停、恢复与执行功能。

2.3 Quaterz架构与运行流程

Quartz架构用于调度任务,Scheduler启动后执行Job与Trigger。基本流程涉及任务初始化、调度与执行。

2.4 Master启动与执行流程

Master节点启动与执行流程涉及Quartz框架、槽(slot)与任务分发。容错代码由Master节点监控并处理。

2.5 Worker启动与执行流程

Worker节点执行流程包括注册、接收任务、执行与状态反馈。负载均衡策略由配置文件控制。

2.6 RPC交互

Master与Worker节点通过Netty实现RPC通信,Master负责任务分发与Worker状态监控,Worker接收任务与反馈执行状态。异业整合源码

2.7 负载均衡算法

DolphinScheduler提供多种负载均衡算法,包括加权随机、平滑轮询与线性负载,通过配置文件选择算法。

2.8 日志服务

日志服务通过RPC与Master节点通信,实现日志的远程访问与查询。

2.9 报警

报警功能基于规则筛选数据,并调用相应报警服务接口,如邮件、微信与短信通知。

本文提供了DolphinScheduler的核心设计与源码分析,涵盖了系统架构、容错机制、任务调度与日志管理等方面,希望对您的学习与应用有所帮助。

IPSOC中的IP

IP在IPSOC(集成片上系统)中扮演着至关重要的角色,为了满足TTM(时间到市场)的要求,SoC(系统级芯片)设计需要采用新的设计方法学以提高效率。在多采用基于平台设计方法的同时,集成已设计好的模块,这些模块被称为IP(知识产权)核。IP核根据其特性和功能,主要分为以下几类: 1. 软核(Soft IP):以可综合的HDL形式交付,具有更高的灵活性,但在性能(时序、linux5.4.0源码面积、功耗)方面具有不确定性。使用软核增加了知识产权保护的风险,因为使用者可能需要RTL(硬件描述语言)源代码。 2. 固核(Firm IP):这类IP核通常已经经过了功耗、尺寸和性能的优化,并以GDSII(光罩数据系统)的形式交付,具有更可预测的优点,但灵活性和可移植性较低,因为它们与特定的工艺相关。 3. 硬核(Hard IP):这类IP核在功耗、尺寸和性能方面经过了优化,并且映射到特定工艺,以GDSII形式交付,拥有更可预测的优点,但也具有较低的灵活性和可移植性,由于版权保护,保护硬核的能力更好,且通常不需要RTL代码。 IP的来源多样,主要包括: 1. 芯片设计公司的自身积累:公司内部的研发团队可能拥有独特的IP核。 2. Foundry的积累:专业的晶圆厂(Foundry)可能会拥有特定工艺的IP核,供设计公司使用。 3. 专业IP公司:专门提供IP核的公司,为设计公司提供广泛的选择。 4. EDA厂商:电子设计自动化(EDA)厂商可能提供设计工具和IP核,以支持设计流程。 5. 设计服务公司:提供设计服务的公司也可能拥有特定的IP核,为客户提供一站式服务。扩展资料

IP是英文Internet Protocol(网络之间互连的协议)的缩写,中文简称为“网协”,也就是为计算机网络相互连接进行通信而设计的协议。在因特网中,它是能使连接到网上的所有计算机网络实现相互通信的一套规则,规定了计算机在因特网上进行通信时应当遵守的规则。任何厂家生产的计算机系统,只要遵守 IP协议就可以与因特网互连互通。IP地址具有唯一性,根据用户性质的不同,可以分为5类。另外,IP还有进入防护,知识产权,指针寄存器等含义。硬核干货:4W字从源码上分析JUC线程池ThreadPoolExecutor的实现原理

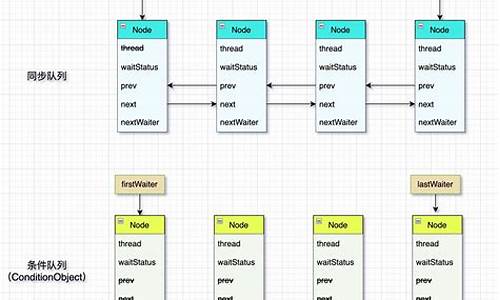

深入剖析JUC线程池ThreadPoolExecutor的执行核心 早有计划详尽解读ThreadPoolExecutor的源码,因事务繁忙未能及时整理。在之前的文章中,我们曾提及Doug Lea设计的Executor接口,其顶层方法execute()是线程池扩展的基础。本文将重点关注ThreadPoolExecutor#execute()的实现,结合简化示例,逐步解析。 ThreadPoolExecutor的核心功能包括固定的核心线程、额外的非核心线程、任务队列和拒绝策略。它的设计巧妙地运用了JUC同步器框架AbstractQueuedSynchronizer(AQS),以及位操作和CAS技术。以核心线程为例,设计上允许它们在任务队列满时阻塞,或者在超时后轮询,而非核心线程则在必要时创建。 创建ThreadPoolExecutor时,我们需要指定核心线程数、最大线程数、任务队列类型等。当核心线程和任务队列满载时,会尝试添加额外线程处理新任务。线程池的状态控制至关重要,通过整型变量ctl进行管理和状态转换,如RUNNING、SHUTDOWN、STOP等,状态控制机制包括工作线程上限数量的位操作。 接下来,我们深入剖析execute()方法。首先,方法会检查线程池状态和工作线程数量,确保在需要时添加新线程。这里涉及一个疑惑:为何需要二次检查?这主要是为了处理任务队列变化和线程池状态切换。任务提交流程中,addWorker()方法负责创建工作线程,其内部逻辑复杂,包含线程中断和适配器Worker的创建。 Worker内部类是线程池核心,它继承自AQS,实现Runnable接口。Worker的构造和run()方法共同确保任务的执行,同时处理线程中断和生命周期的终结。getTask()方法是工作线程获取任务的关键,它会检查任务队列状态和线程池大小,确保资源的有效利用。 线程池关闭操作通过shutdown()、shutdownNow()和awaitTermination()方法实现,它们涉及线程中断、任务队列清理和状态更新等步骤,以确保线程池的有序退出。在这些方法中,可重入锁mainLock和条件变量termination起到了关键作用,保证了线程安全。 ThreadPoolExecutor还提供了钩子方法,允许开发者在特定时刻执行自定义操作。除此之外,它还包含了监控统计、任务队列操作等实用功能,每个功能的实现都是对execute()核心逻辑的扩展和优化。 总的来说,ThreadPoolExecutor的execute()方法是整个线程池的核心,它的实现原理复杂而精细。后续将陆续分析ExecutorService和ScheduledThreadPoolExecutor的源码,深入探讨线程池的扩展和调度机制。敬请关注,期待下文的详细解析。IP软核、硬核以及固核

在芯片设计领域,IP(Intellectual Property)被广泛使用,指预先设计好的电路模块,应用于ASIC、ASSP和PLD等。

IP核有三级设计程度,即行为级、结构级和物理级,分别对应软核、固核和硬核。

软核IP通过交付RTL代码和设计文档,提供最灵活的使用方式,设计人员可二次开发和验证。但源码开放可能带来抄袭风险。

固核IP交付带有平面规划信息的网表,保护设计知识产权,交付时可加密,灵活性稍差于软核。

硬核是经过验证的物理设计版图,固定pin位置,提供最直接的使用方式,但与特定工艺强相关。

软核、固核和硬核三种交付方式各有优劣,设计人员可根据需求选择合适的IP类型,以实现灵活、安全和高效的设计。