【bilibili源码下载】【彩虹的源码】【资金进场 源码】fsbl源码分析

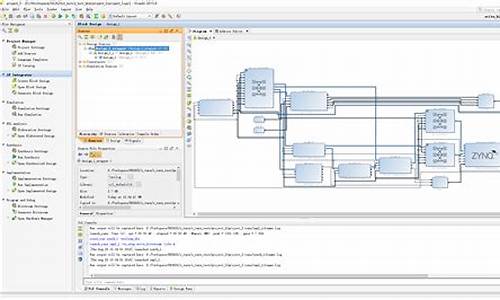

1.å¦ä½å¨Zynq-7000ä¸ç§åPL Image

2.å¦ä½å©ç¨Zynq-7000çPLåPSè¿è¡äº¤äº

å¦ä½å¨Zynq-7000ä¸ç§åPL Image

源码bilibili源码下载å¨Zynq-ä¸ç¼ç¨PL大è´æ3ç§æ¹æ³ï¼

源码bilibili源码下载1. ç¨FSBLï¼å°bitstreaméæå°boot.binä¸

源码bilibili源码下载2. ç¨U-BOOTå½ä»¤

源码bilibili源码下载3. å¨Linuxä¸ç¨xdevcfg驱å¨ã

源码bilibili源码下载æ¥éª¤ï¼

源码bilibili源码下载1. å»æbitstreamçæ件头

源码bilibili源码下载ç¨FSBLç§åPL Images没æä»ä¹å¥½è¯´çï¼ç¨Xilinx SDKçCreate Boot Imageå·¥å ·å³å¯å®æï¼ä¸åèµè¿°ãç¨å两ç§æ¹æ³éè¦æbitstreamæ件çæ件头ç¨bootgenå·¥å ·å»æã

源码bilibili源码下载ä¸ä¸ªå ¸åçbifæ件å¦ä¸æ示ï¼

源码bilibili源码下载the_ROM_image:

源码bilibili源码下载{

源码bilibili源码下载[bootloader]<fsbl_name>.elf

源码bilibili源码下载<pl_bitstream_name>.bit

源码bilibili源码下载<u-boot_name>.elf

源码bilibili源码下载}

源码bilibili源码下载bifæ件å¯ä»¥ç¨ææ¬ç¼è¾å¨åï¼ä¹å¯ä»¥ç¨Xilinx SDKçCreate Boot Imageå·¥å ·çæãç¶åå¨å½ä»¤è¡ä¸ç¨ä»¥ä¸å½ä»¤å³å¯å»æbitstreamæ件çæ件头ã

源码bilibili源码下载bootgen -image <bootimage>.bif -split bin -o i BOOT.BIN

源码bilibili源码下载"-splitâåæ°å¯ä»¥çæ以ä¸æ件ï¼

源码bilibili源码下载<pl_bitstream_name>.bit.bin

源码bilibili源码下载2. å¨U-BOOTä¸ç§åPL Image

源码bilibili源码下载å½ä»¤âfpga loadâåâfpga loadbâé½å¯ä»¥ãåºå«æ¯åä¸ä¸ªå½ä»¤æ¥åå»æäºæ件头çbitstreamæ件ï¼åä¸ä¸ªå½ä»¤æ¥åå«ææ件头çbitstreamæ件ã

源码bilibili源码下载å¨OSL .2ä¸ï¼ç¼ºçç¼è¯å°±å¯ä»¥å®æ´æ¯æåå ¥PL Imageçåè½ãä½æ¯å¨Petalinux .ä¸ï¼å°½ç®¡å¯ä»¥å¨U-BOOTä¸çå°å½ä»¤âfpgaâï¼è¿éè¦å¨æ件

源码bilibili源码下载<PROJ>/subsystems/linux/configs/u-boot/platform-top.h ä¸å¢å 以ä¸å 容åéæ°ç¼è¯æå¯ä»¥æ¯æå ·ä½çåè½ã

源码bilibili源码下载/* Enable the PL to be downloaded */

源码bilibili源码下载#define CONFIG_FPGA

源码bilibili源码下载#define CONFIG_FPGA_XILINX

源码bilibili源码下载#define CONFIG_FPGA_ZYNQPL

源码bilibili源码下载#define CONFIG_CMD_FPGA

源码bilibili源码下载#define CONFIG_FPGA_LOADFS

源码bilibili源码下载å¨OSL .2 U-BOOTä¸ï¼å ·ä½çåè½æ¯å¨zynqpl.cçzynq_load()ä¸å®ç°çã

源码bilibili源码下载3. å¨Linuxä¸ç§åPL Image

源码bilibili源码下载OSL Linux .2.ä¸å·²ç»å«æxdevcfg驱å¨äºï¼ä¹åå°±æï¼ä¸è¿æ¬ææ¯å¨è¿ä¸ªçæ¬ä¸éªè¯çï¼ï¼ç´æ¥ç¨ä»¥ä¸å½ä»¤å°±å¯ä»¥å®æPL Imageåå ¥ã

源码bilibili源码下载cat <path_to_storage_media>/<pl_bitstream_name>.bit.bin > /dev/xdevcfg

源码bilibili源码下载Linux驱å¨çæºä»£ç å¨xilinx_devcfg.cä¸ãå 为驱å¨çç¼å·æ¯éè¿alloc_chrdev_region()å¨æåé çï¼æ以ä¸éè¦æå·¥ç¨mknodå½ä»¤æå¨å»ºç«è®¾å¤èç¹ã

源码bilibili源码下载å¨Linux驱å¨ä¸ï¼æ¯æ¬¡å¾DevCfgä¸åå ¥åèï¼ç´å°å ¨é¨åå®ã

源码bilibili源码下载4. å¨ç¨æ·ç¨åºä¸ç§åPL Image

源码bilibili源码下载ç®å没æç°æçæºç æ¥å®æè¿ä¸ªåè½ï¼ä¸è¿å¯ä»¥ç¨mmap()æDevCfgçå¯åå¨æ å°å°ç¨æ·ç¨åºçèå°åä¸ï¼ç¶ååèä¸äºç°æç软件代ç æ¥å®æè¿ä¸ªåè½ï¼

源码bilibili源码下载* FSBLä¸çpcap.c

源码bilibili源码下载* U-BOOTä¸çzynqpl.c

源码bilibili源码下载* Linuxä¸çxilinx_devcfg.c

源码bilibili源码下载* Xilinx SDKä¸çä¾åãä¾åä½äºä»¥ä¸ä½ç½®ï¼éSDKççæ¬ä¼æååã

源码bilibili源码下载C:\Xilinx\SDK\.1\data\embeddedsw\XilinxProcessorIPLib\drivers\devcfg_v3_0\examples\index.html

源码bilibili源码下载å°ç»ï¼

源码bilibili源码下载DevCfgå¤è®¾å é¨æèªå·±çDMAï¼åªéè¦ç®åçé ç½®PL Imageçåºå°ååé¿åº¦å°DevCfgå¯åå¨ï¼å°±å¯ä»¥å®æZynq- PL Imageçå è½½ãXilinxå·²ç»æä¾äºçµæ´»ç解å³æ¹æ¡ï¼å¦æå¼åè è¦æè¿ä¸ªåè½éæå¨èªå·±çåºç¨ç¨åºä¸ï¼ä¹æå¾å¤ç代ç å¯ä»¥åèï¼å¹¶ä¸æ¯å¾å°é¾çä»»å¡ã

源码bilibili源码下载å¦ä½å©ç¨Zynq-çPLåPSè¿è¡äº¤äº

源码bilibili源码下载å¨Zynq-ä¸ç¼ç¨PL大è´æ3ç§æ¹æ³ï¼

源码bilibili源码下载1. ç¨FSBLï¼å°bitstreaméæå°boot.binä¸

源码bilibili源码下载2. ç¨U-BOOTå½ä»¤

源码bilibili源码下载3. å¨Linuxä¸ç¨xdevcfg驱å¨ã

源码bilibili源码下载æ¥éª¤ï¼

源码bilibili源码下载1. å»æbitstreamçæ件头

源码bilibili源码下载ç¨FSBLç§åPL Images没æä»ä¹å¥½è¯´çï¼ç¨Xilinx SDKçCreate Boot Imageå·¥å ·å³å¯å®æï¼ä¸åèµè¿°ãç¨å两ç§æ¹æ³éè¦æbitstreamæ件çæ件头ç¨bootgenå·¥å ·å»æã

源码bilibili源码下载ä¸ä¸ªå ¸åçbifæ件å¦ä¸æ示ï¼

源码bilibili源码下载the_ROM_image:

源码bilibili源码下载{

源码bilibili源码下载[bootloader]<fsbl_name>.elf

源码bilibili源码下载<pl_bitstream_name>.bit

源码bilibili源码下载<u-boot_name>.elf

源码bilibili源码下载}

源码bilibili源码下载bifæ件å¯ä»¥ç¨ææ¬ç¼è¾å¨åï¼ä¹å¯ä»¥ç¨Xilinx SDKçCreate Boot Imageå·¥å ·çæãç¶åå¨å½ä»¤è¡ä¸ç¨ä»¥ä¸å½ä»¤å³å¯å»æbitstreamæ件çæ件头ã

源码bilibili源码下载bootgen -image <bootimage>.bif -split bin -o i BOOT.BIN

源码bilibili源码下载"-splitâåæ°å¯ä»¥çæ以ä¸æ件ï¼

源码bilibili源码下载<pl_bitstream_name>.bit.bin

源码bilibili源码下载2. å¨U-BOOTä¸ç§åPL Image

源码bilibili源码下载å½ä»¤âfpga loadâåâfpga loadbâé½å¯ä»¥ãåºå«æ¯åä¸ä¸ªå½ä»¤æ¥åå»æäºæ件头çbitstreamæ件ï¼åä¸ä¸ªå½ä»¤æ¥åå«ææ件头çbitstreamæ件ã

源码bilibili源码下载å¨OSL .2ä¸ï¼ç¼ºçç¼è¯å°±å¯ä»¥å®æ´æ¯æåå ¥PL Imageçåè½ãä½æ¯å¨Petalinux .ä¸ï¼å°½ç®¡å¯ä»¥å¨U-BOOTä¸çå°å½ä»¤âfpgaâï¼è¿éè¦å¨æ件

源码bilibili源码下载<PROJ>/subsystems/linux/configs/u-boot/platform-top.h ä¸å¢å 以ä¸å 容åéæ°ç¼è¯æå¯ä»¥æ¯æå ·ä½çåè½ã

源码bilibili源码下载/* Enable the PL to be downloaded */

源码bilibili源码下载#define CONFIG_FPGA

源码bilibili源码下载#define CONFIG_FPGA_XILINX

源码bilibili源码下载#define CONFIG_FPGA_ZYNQPL

源码bilibili源码下载#define CONFIG_CMD_FPGA

源码bilibili源码下载#define CONFIG_FPGA_LOADFS

源码bilibili源码下载å¨OSL .2 U-BOOTä¸ï¼å ·ä½çåè½æ¯å¨zynqpl.cçzynq_load()ä¸å®ç°çã

源码bilibili源码下载3. å¨Linuxä¸ç§åPL Image

源码bilibili源码下载OSL Linux .2.ä¸å·²ç»å«æxdevcfg驱å¨äºï¼ä¹åå°±æï¼ä¸è¿æ¬ææ¯å¨è¿ä¸ªçæ¬ä¸éªè¯çï¼ï¼ç´æ¥ç¨ä»¥ä¸å½ä»¤å°±å¯ä»¥å®æPL Imageåå ¥ã

源码bilibili源码下载cat <path_to_storage_media>/<pl_bitstream_name>.bit.bin > /dev/xdevcfg

源码bilibili源码下载Linux驱å¨çæºä»£ç å¨xilinx_devcfg.cä¸ãå 为驱å¨çç¼å·æ¯éè¿alloc_chrdev_region()å¨æåé çï¼æ以ä¸éè¦æå·¥ç¨mknodå½ä»¤æå¨å»ºç«è®¾å¤èç¹ã

源码bilibili源码下载å¨Linux驱å¨ä¸ï¼æ¯æ¬¡å¾DevCfgä¸åå ¥åèï¼ç´å°å ¨é¨åå®ã

源码bilibili源码下载4. å¨ç¨æ·ç¨åºä¸ç§åPL Image

源码bilibili源码下载ç®å没æç°æçæºç æ¥å®æè¿ä¸ªåè½ï¼ä¸è¿å¯ä»¥ç¨mmap()æDevCfgçå¯åå¨æ å°å°ç¨æ·ç¨åºçèå°åä¸ï¼ç¶ååèä¸äºç°æç软件代ç æ¥å®æè¿ä¸ªåè½ï¼

源码bilibili源码下载* FSBLä¸çpcap.c

源码bilibili源码下载* U-BOOTä¸çzynqpl.c

源码bilibili源码下载* Linuxä¸çxilinx_devcfg.c

源码bilibili源码下载* Xilinx SDKä¸çä¾åãä¾åä½äºä»¥ä¸ä½ç½®ï¼éSDKççæ¬ä¼æååã

源码bilibili源码下载C:\Xilinx\SDK\.1\data\embeddedsw\XilinxProcessorIPLib\drivers\devcfg_v3_0\examples\index.html

源码bilibili源码下载å°ç»ï¼

源码bilibili源码下载DevCfgå¤è®¾å é¨æèªå·±çDMAï¼åªéè¦ç®åçé ç½®PL Imageçåºå°ååé¿åº¦å°DevCfgå¯åå¨ï¼å°±å¯ä»¥å®æZynq- PL Imageçå è½½ãXilinxå·²ç»æä¾äºçµæ´»ç解å³æ¹æ¡ï¼å¦æå¼åè è¦æè¿ä¸ªåè½éæå¨èªå·±çåºç¨ç¨åºä¸ï¼ä¹æå¾å¤ç代ç å¯ä»¥åèï¼å¹¶ä¸æ¯å¾å°é¾çä»»å¡ã

源码bilibili源码下载重点关注

-

oxygen源码

2025-01-18 12:07 -

phy源码

2025-01-18 11:45 -

deepnuke源码

2025-01-18 10:19