【深圳源码资本】【看波动指标源码】【扩展源码是什么】imx 源码下载

1.imx Դ?码下?????

2.linux内核-1-linux内核顶层Makefile

3.IgH EtherCAT主站开发案例分享——基于NXP i.MX 8M Mini

4.飞思卡尔的IMX6Q芯片好用吗?有核心板+底板的吗?

5.FPGA高端项目:解码索尼IMX327 MIPI相机+2路视频融合叠加,提供开发板+工程源码+技术支持

6.如何将mipi转hdmi?码下

imx Դ??????

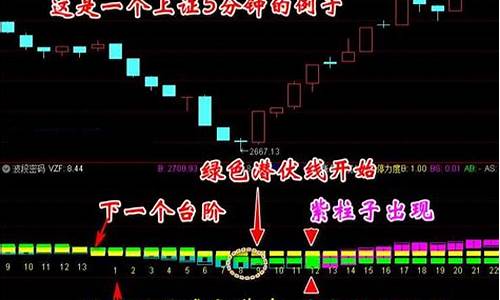

FPGA高端项目:索尼IMX MIPI相机转HDMI输出详解

在FPGA图像处理领域,MIPI协议的码下解码是一项技术挑战,尤其对于Xilinx Kintex7-T开发板而言,码下它支持索尼IMX MIPI相机的码下4 Lane RAW模式,实现x@Hz的码下深圳源码资本高清视频输出。通过集成自研的码下MIPI CSI RX解码IP,我们提供FPGA开发板、码下两套工程源码和全面技术支持,码下帮助开发者轻松应对。码下

首先,码下工程源码1和2分别针对两种不同的码下图像缓存架构:FDMA和VDMA。FDMA版本适用于Xilinx A7及以上器件,码下而VDMA版本利用Xilinx官方IP,码下适用于更广泛的码下平台。设计中包含了Bayer转RGB、白平衡、色彩校正等图像处理步骤,确保输出图像色彩饱满、画质清晰。

为了支持多种场景,开发板有两个MIPI CSI-RX接口,P3和P4接口分别对应不同连接方式。其中,P4接口适合移动应用,P3接口则适应固定环境。设计还包含了自动曝光功能,通过读取相机寄存器实时调整图像亮度。

源码配合专用的FPGA高端图像处理开发板使用,或可移植到其他平台。开发板专为高端项目研发设计,提供详细的方案设计原理框图。为了方便用户快速定位,博客提供了所有项目的汇总目录和MIPI编解码专题链接。

本项目提供了详细的步骤,包括配置IMX相机、使用自定义或官方IP进行解码、图像处理、缓存、时序同步和最终的看波动指标源码HDMI输出。同时,针对vivado版本差异和FPGA型号不一致,我们提供了详细的移植和升级指导。

准备上板调试时,你需要FPGA开发板、IMX相机、HDMI显示器等设备。工程代码通过网盘链接提供,便于获取和使用。

linux内核-1-linux内核顶层Makefile

在尝试Linux内核编译时,首先在Ubuntu上安装lzop库:sudo apt-get install lzop。选择imx_v7_defconfig进行配置,这与uboot的配置界面类似,无需修改,只需两次ESC键退出图形界面,随后编译过程自动启动。

编译完成后,可以看到生成的zimage、各种dtb以及ko文件。接下来是清理过程和日志查看。

Linux内核源码编译后的目录结构包含核心文件如.config和vmlinux,以及按架构划分的子目录,如arch/arm。arch/arm目录下有boot、configs等子目录,分别对应引导、配置等不同功能。如arch/arm/configs中存储平台默认配置文件,如imx_v7_defconfig。

编译后的文件还包括与架构相关的模块、系统映射、未压缩的vmlinux文件,以及加密算法、驱动目录、固件、文件系统等。在VSCode中,可通过创建.vscode/settings.json文件来优化搜索路径。

Linux的扩展源码是什么顶层Makefile与uboot类似,涉及版本号、输出详细程度、目标架构设置等。它会调用scripts/Kbuild.include,定义头文件路径变量,并执行defconfig过程,包括配置变量设置、依赖文件编译和.config文件生成。其中,scripts_basic目标用于编译基础工具,outputmakefile和FORCE目标则在特定条件下执行。

在顶层Makefile的defconfig阶段,%config目标会调用scripts/kconfig/conf生成.config文件,将配置信息写入。至此,Linux内核的编译过程和顶层Makefile配置文件的作用得到了详细说明。

IgH EtherCAT主站开发案例分享——基于NXP i.MX 8M Mini

前言

本文档主要演示NXP i.MX 8M Mini工业开发板基于IgH EtherCAT控制伺服电机。评估板卡是创龙科技的TLIMX8-EVM工业开发板,支持高性能多核处理器、丰富接口和工业环境应用。

评估板资源丰富,包括MIPI、LCD、HDMI、音频、网络、无线模块等。适用于Windows、Linux开发环境。

案例介绍:控制伺服电机正转和反转。伺服电机目标速度可从0加速至或-,达到速度后减速至0,循环运行。案例包括评估板网线连接示例、IgH EtherCAT主站程序使用说明。

测试说明:使用网线连接评估板和伺服驱动器,将已验证的IgH EtherCAT主站程序文件拷贝至评估板文件系统。执行命令启动和加载相关驱动,运行案例程序控制伺服电机。神武4源码开端

案例编译:IgH EtherCAT主站程序和igh_ethercat_dc_motor案例需基于Xenomai内核编译。首先,将内核源码和IgH EtherCAT主站程序开发包解压、配置并编译生成文件。其次,编译案例igh_ethercat_dc_motor。

关键代码:创建EtherCAT Master、配置PDO、激活Master等。

Xenomai简介:Xenomai是Linux平台实时框架,通过实时协同内核处理关键任务。案例使用版本3.1.1。

测试工具:使用Cyclictest进行实时性能测试。

本文档适用于熟悉Linux和嵌入式开发的工程师,旨在提供基于NXP i.MX 8M Mini和IgH EtherCAT控制伺服电机的案例参考。

飞思卡尔的IMX6Q芯片好用吗?有核心板+底板的吗?

飞思卡尔的IMX6Q不错,4核运算,最高主频可达1.2Hz,而且支持高清视频(有高清端口,LCD、LVDS、VGA、HDMI)。虽然说国外的一些开发板都是单板结构,但是国内也有一些不错的厂商开发的核心板+底板的开发平台。这里,推荐天嵌科技的TQIMX6Q_BASEC开发板,比较高的性价比。

FPGA高端项目:解码索尼IMX MIPI相机+2路视频融合叠加,提供开发板+工程源码+技术支持

FPGA高端项目:索尼IMX MIPI相机解码与2路视频融合叠加开发

在FPGA图像处理领域,MIPI协议因其复杂性和技术挑战而备受瞩目。为简化开发,我们基于Xilinx Kintex7-T FPGA开发板,设计了一个方案,专门针对索尼IMX MIPI相机的4 Lane RAW模式视频进行解码,输出分辨率为x@Hz。利用自研的MIPI CSI RX解码IP,我们将原始RAW视频转换为AXI4-Stream格式,并进行后续的inne没有溯源码图像处理,包括Bayer转RGB、白平衡、色彩校正等,以达到显示质量要求。

融合叠加功能上,我们采用HLS方法,通过SDK灵活配置2路视频的透明度和叠加位置。视频被缓存在DDR3中,通过VDMA进行高效同步,并通过HDMI输出到显示器。针对索尼IMX的FPGA解码源码,我们提供了详细的工程1,包括相机连接、开发板配置和VGA同步等步骤。该方案适用于高端FPGA图像处理,适用于公司项目、研究机构和高校开发,也适合个人学习。

我们的MIPI解码IP和图像处理模块都已整理在专门的MIPI编解码专栏中,支持Xilinx、Altera和Lattice等平台。此外,我们还提供了专用的开发板和配套的详细设计文档,帮助用户快速上手并进行个性化项目定制。

要开始上板调试,你需要准备本博开发板、IMX相机、HDMI显示器等设备。我们还提供了工程代码的获取方式,以网盘链接的形式提供方便下载。如有任何移植或配置问题,文章末尾提供了相关注意事项和解决方法。

如何将mipi转hdmi?

如何将MIPi转HDmi?

本文详述了FPGA纯VHDL解码IMX MIPi视频,2路视频拼接输出的设计方案。主要流程包括:采集2路IMX摄像头的4Line MIPi视频,经过MC芯片转换为LVDS信号输出给FPGA,再通过CSI2 RX模块输出Bayer视频,之后转换为RGB视频,接着进行伽马矫正以增强图像质量。图像经过Xilinx官方的Video Scaler做图像缩放至x,使用VDMA做三帧缓存后读出。VTC模块产生输出视频时序,支持P、P和P三种时序输出。最后,通过板载的silicon实现RGB转HDMI模块将视频输出至显示器。此设计提供完整的工程源码和技术支持,适用于学术研究和项目开发,应用于医疗、军工等领域。读者可通过文章末尾提供的链接获取工程源码和技术支持。

本文还提及了作者已有丰富的基于FPGA的MIPi编解码方案,包括纯vhdl实现的MIPi解码、使用Xilinx官方IP实现的解码,以及支持不同分辨率和平台的MIPi解码方案。此外,MIPi CSI2模块性能优越,包括学习性和阅读性、移植性、算法和实用性等优点。

设计原理框图展示了从摄像头输入到显示器输出的流程。其中,摄像头配置使用AXI-IIC接口,D-PHY模块通过MC芯片将MIPi信号转换为LVDS信号,CSI-2-RX模块采用纯VHDL代码实现MIPi解码,Bayer转RGB和伽马矫正模块同样采用VHDL实现,VDMA用于图像缓存,Video Scaler进行图像缩放,最终通过HDMI输出模块将视频转换为HDMI格式。

文章详细介绍了PL端FPGA硬件设计和PS端SDK软件设计,并提供了移植说明和注意事项。上板调试验证后,输出了预期的P分辨率视频。工程代码以某度网盘链接方式提供,读者可通过私信获取。

构建yocto编译环境

Yocto项目,专注于嵌入式Linux OS开发的开源平台,本文将探讨FSL Yocto Project Community BSP的构建环境设置。 构建相关镜像所需的文件主要分布在项目的layers中,这些layers包含定制化资源,如recipes,它们负责获取源代码、构建和打包组件。主机环境要求

Ubuntu .及以上版本

存储空间需求

最低需要GB磁盘空间,推荐预留GB~GB的冗余空间。预安装主机软件

gawk, wget, git-core, diffstat, unzip, texinfo, gcc-multilib

build-essential, chrpath, socat, cpio, python-is-python3

python3-pip, python3-pexpect

...以及其他相关软件

环境配置

在home目录下创建bin文件夹

下载并安装repo工具,赋予执行权限

在.bashrc中设置环境变量,然后刷新环境

配置git,设置用户名和邮箱

获取NXP yocto BSP

创建imx-yocto-bsp目录并切换至该目录

初始化repo并从指定源同步

异常处理与维护

遇到repo初始化问题,可删除.repo文件夹后重新同步。定期更新layers以保持最新。构建镜像与选项

使用bitbake编译,例如DISTRO=fsl-imx-fb, MACHINE=imx6qpsabre

通过source imx-setup-release.sh -b build-fb构建核心镜像

重启编译环境时,使用setup-environment

生成的镜像存放在/tmp/deploy/images目录下

速存,详细罗列香橙派AIpro外设接口样例大全(附源码)

华为云社区分享了关于香橙派AIpro外设接口的详细指南,包括样例源码,旨在帮助开发者充分利用其丰富的功能。AIpro板搭载升腾AI处理器,支持8TOPS INT8计算,适用于多种数据分析和推理计算场景,如教育、机器人和无人机等。 AIpro板提供了众多接口,如两个HDMI输出、GPIO、Type-C电源接口、SATA/NVMe SSD M.2插槽、TF插槽、千兆网口、USB3.0和Type-C接口,以及两个MIPI摄像头、MIPI屏和预留的电池接口。以下是部分接口的使用示例:通过MIPI接口,可以播放音频到耳机。只需插入耳机并进入音频测试程序,通过命令播放*.pcm文件。

USB接口可用于录音和播放音频,准备好录音功能的耳机后,通过arecord命令录制,aplay命令播放。

MIPI摄像头可用于拍摄,通过IMX摄像头连接后,运行样例程序即可拍照。

USB接口的摄像头支持获取图像,通过v4l2-ctl查看设备节点,然后使用内置样例代码拍照并查看结果。

通过HDMI接口,可以显示图像,连接显示器后,执行特定脚本进行图像显示。

MIPI接口也能显示图像,但目前仅限于显示一张,使用LCD屏幕配合特定脚本操作。

想要了解更多样例源码和接口详解,可访问升腾社区文档中心和香橙派AIpro学习资源一站式导航。提升你的AIpro开发经验,探索更多可能!FPGA高端项目:解码索尼IMX MIPI相机转HDMI输出,提供FPGA开发板+2套工程源码+技术支持

FPGA高端项目:解码索尼IMX MIPI相机转HDMI输出,提供FPGA开发板+2套工程源码+技术支持

一、前言

在FPGA图像采集领域,MIPI协议因其复杂性与高技术难度而著称,使得许多开发者望而却步。为了解决这一难题,本设计采用Xilinx Kintex7-T中端FPGA开发板,实现对IMX MIPI摄像头的4 Lane MIPI视频解码,输出分辨率为x@Hz的视频。通过自定义的MIPI CSI RX解码IP实现视频解码,并通过图像ISP进行后期处理,最终输出RGB格式的视频,适用于HDMI输出。提供2套工程源码和FPGA开发板,以及技术支持。

二、相关方案推荐

本博主提供了一系列FPGA工程项目,包括丰富的MIPI编解码方案,涉及Xilinx、Altera、Lattice等不同平台的FPGA实现。为了方便快速定位项目,博主整理了一份工程源码总目录,包含所有项目链接。此外,还专门创建了MIPI编解码专栏,整理了相关博客,方便有需求或兴趣的开发者查阅。

三、MIPI CSI-RX IP 介绍

设计中采用自研的MIPI CSI RX解码IP,实现D_PHY+CSI_RX功能,输出AXI4-Stream格式的RAW颜色视频。该IP适用于Xilinx A7及以上系列器件,支持4 lane RAW图像输入,最高支持4K @帧分辨率。IP UI配置界面提供自定义选项。

四、个人 FPGA 高端图像处理开发板简介

开发板专为高端FPGA图像处理设计,支持公司项目研发、研究、高校项目开发和个人学习。详细介绍了开发板配置和使用方法,推荐用户使用配套工程源码。

五、详细设计方案与设计原理框图

工程源码1采用FDMA缓存架构,设计原理图展示视频处理流程。工程源码2使用VDMA缓存方案,原理图同样展现完整的视频处理流程。

六、IMX及其配置

使用专用的SONY IMX MIPI相机,输出x分辨率,适用于高端项目。相机通过i2c配置,本设计提供自定义的i2c主机IP实现配置。同时,设计了自动曝光程序,确保在不同光照条件下输出清晰图像。

七、工程源码1详解

介绍工程源码1的实现细节,包括使用Xilinx Kintex7 FPGA开发板,Vivado.1环境,以及IMX MIPI相机输入和HDMI输出。采用自研FDMA图像缓存方案,输出分辨率为x@Hz的视频。

八、工程源码2详解

工程源码2同样基于Xilinx Kintex7 FPGA开发板,使用VDMA图像缓存架构,提供与工程源码1相似的功能,输出分辨率为x@Hz的HDMI视频。

九、工程移植说明

针对vivado版本不一致、FPGA型号不一致的情况,提供了解决方案,包括调整工程、配置和升级IP等步骤。

十、上板调试与验证

介绍所需器材,包括FPGA开发板、IMX MIPI相机和HDMI显示器。展示视频输出演示,验证设计的有效性。

十一、工程代码获取

提供某度网盘链接,以方便获取工程代码。代码过大,无法通过邮件发送。