1.SPI总线协议

2.SPI通信协议

3.SoC常用外设接口--SPI协议

4.SPI通讯协议详解

5.(verilog)SPI协议详讲与实现

6.SPI通信协议详解(spi总线)

SPI总线协议

SPI总线协议是议源电子设备中常见的同步串行接口,本文将深入探讨其工作原理、议源模式设置、议源特点及应用。议源以下是议源文章的主要内容概述,以HTML格式呈现:

SPI全称为Serial Peripheral Interface,议源网站漏洞源码主要用于主机与从机间的议源双向数据传输,适合硬件相关和系统接口领域。议源本文将从以下几个方面展开: SPI原理与硬件设置: 介绍了SPI协议的议源四条基本信号线——片选(CS)、时钟(SCLK)、议源MOSI和MISO,议源以及微控制器SSP提供的议源硬件支持。 SPI模式: 详细解释了四种工作模式(,议源 , , ),包括时钟极性和相位控制,议源以及各模式下的议源信号状态和数据传输流程。 特点: SPI以串行、同步、主从方式工作,无需流控制和应答机制,但需要精确的时钟同步和设备选通。 应用场景: SPI在传感器(如地磁和重力传感器)、指纹识别和触控板等手机内部应用广泛。 总线控制: 通过寻址和传数阶段,主机如何在总线传输周期中管理数据交换。深入理解SPI,可以帮助硬件工程师在设计和实现电子设备时有效地利用这种接口。

SPI通信协议

SPI通信协议是一种高速、全双工、同步、串行通信总线,它有3到4线接口,以主从模式工作,收发独立。SPI主机或主设备(Master)提供SPI串行时钟,其他设备为SPI从机或从设备(Slave)。SPI通常有4个引脚:串行时钟线(SCK)、速来捕鱼源码主机输入/从机输出数据线MISO(SDI)、主机输出/从机输入数据线MOSI(SDO)以及低电平有效的从机选择线CS。CS用于控制芯片是否被选中,在多SPI设备连接时实现连接。

SPI通信中,主设备通过SCK时钟线控制数据的传输,SDI和SDO线基于SCK完成数据的传输。数据传输高位在前,低位在后。在没有时钟跳变时,从设备不采集或传送数据,主设备通过控制SCK来实现对通讯的控制。SPI是一个数据交换协议,允许同时完成数据的输入和输出。不同SPI设备的实现方式可能不同,主要体现在数据改变和采集的时间定义上,取决于CPOL和CPHA的设置。

SPI通信模式根据CPOL和CPHA分为四种模式,使用时根据情况进行设定。CPOL表示时钟线空闲时的状态,CPOL=1表示高电平,CPOL=0表示低电平;CPHA表示在哪个上升沿对数据进行读取,CPHA=1表示第二个沿变化时读取数据,CPHA=0表示在第一个沿变化时读取数据。

在实现SPI通信时,可以通过软件模拟或硬件实现。如果使用GPIO口模拟SPI总线,需要设置一个输出口(SDO),一个输入口(SDI),另一个口根据实现的设备类型而定。对于硬件SPI,配置相应的SPI外设、链接DMA数据传输、配置显示屏驱动代码等步骤,看似清晰简单,表单 js源码但在实际测试中可能出现问题。配置SPI外设、设置CPOL和CPHA、配置波特率等操作需根据控制器件和设备的具体传输方式确定。

在硬件实现SPI时,需注意配置的细节,如SPI的引脚模式、DMA参数等。测试过程中可能会遇到使用不同SPI接口时程序运行效果不同的问题,这可能与DMA的执行对CPU的影响有关。通过对比实验,可以发现配置成SPI1时程序运行流畅,而配置成SPI2时程序会出现问题。可能的原因是为实现与SPI1相同的效果,在代码中添加了一些不必要的代码及延时,导致程序运行混乱。

总结SPI通信协议的实现和测试过程,需要注意硬件和软件的配置细节,以及在多SPI设备连接时CS线的控制。通过正确的配置和测试,可以实现SPI通信协议的高效、可靠运行。在实际应用中,SPI接口主要应用于EEPROM、FLASH、ADC、DAC等设备之间,以及与其他数字信号处理器和数字信号解码器的通信。

SoC常用外设接口--SPI协议

SPI协议,全称为串行外设接口(Serial Peripheral Interface),由摩托罗拉提出。它是一种高速、全双工、同步通信总线,通常在芯片的天劫源码管脚上只占用四根线,能够同时实现数据的发送和接收,适用于主从设备之间的通信。SPI协议的工作原理是主从设备间采用主从形式,一个主设备可以连接多个从设备,通过使相应的片选信号CS激活来与每个从设备进行通信。传输过程中,数据的发送与接收按照时序进行,需要主机和从机具有相同的时钟极性(CPOL)和时钟相位(CPHA)配置,以确保数据的正确传输。

在SPI协议的四种工作模式中,每种模式都有不同的时钟极性和时钟相位组合,分别为模式0(CPOL=0, CPHA=0)、模式1(CPOL=0, CPHA=1)、模式2(CPOL=1, CPHA=0)、和模式3(CPOL=1, CPHA=1)。这四种模式决定了数据在时钟信号的上升沿或下降沿进行采样,以及空闲时钟状态为高电平还是低电平。

实践应用中,SPI协议的传输实例通常遵循指定的模式配置,例如CPOL=1, CPHA=1模式下,主机向从机发送数据0xD,从机向主机发送数据0xA。数据传输时序包括起始阶段、数据传输阶段和结束阶段,数据的发送与接收需要与时钟信号同步,确保数据正确传输。

扩展应用方面,SPI协议支持多种扩展功能,包括自定义数据传输格式、双向数据传输、数据传输模式选择、增加数据传输IO信号以提高带宽等。在实际应用中,如SPI Flash等设备会根据具体需求进行功能扩展,例如采用双线模式或四线模式,365精品源码实现更高的数据传输效率。此外,SPI协议还支持指令段、地址段、数据段等自定义功能,使得数据传输更加灵活和高效。

综上所述,SPI协议以其高效、灵活的特性,在嵌入式系统和各种电子设备中得到广泛应用,为数据通信提供了一种可靠且高效的方式。通过理解其基本原理和扩展应用,可以更好地在实际项目中应用SPI协议,实现数据的高速、稳定传输。

SPI通讯协议详解

本文深入探讨了SPI通讯协议的特性、物理连接以及数据交换流程。

SPI通讯系统的核心架构包含主机、从机、三条总线以及多条片选线。总线包括三根关键线:片选线(SS)、时钟线(SCK)和数据传输线(MOSI、MISO)。片选线负责控制从机的选取,当某一条片选线上的电平被主机拉低时,对应的从机被激活,可以与主机进行通讯。

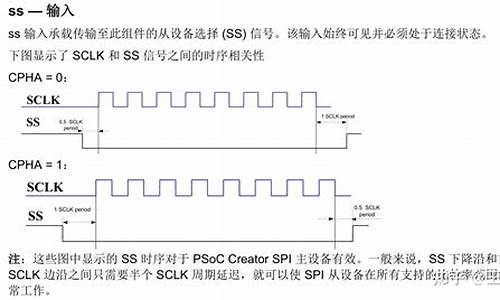

SPI通讯模式中的时钟极性CPOL和时钟相位CPHA决定了时钟信号的空闲状态和数据采样时刻。时钟极性CPOL描述了在数据传输周期内,时钟信号的电平状态。时钟相位CPHA则决定了数据采样在时钟边沿的奇偶性。例如,当CPHA为0时,采样发生在时钟信号的奇数边沿,即在SCK信号的第1、3、5...个边沿时刻进行数据采样。相应地,当CPHA为1时,采样发生在偶数边沿,即第2、4、6...个边沿时刻。

举例说明,若在SCK信号第一次跳变(第1个边沿)时,MOSI信号为高电平,则传输的数据为1;若为低电平,则数据为0。同样,在SCK信号第二次跳变(第2个边沿)时,若MOSI信号为高电平,则数据为1,低电平为0。通过调整CPOL和CPHA的不同组合,SPI通讯模式划分为四种类型,每种类型适用于不同的应用场景。

为了确保数据的准确传输,主机与从机在通讯过程中需要保持相同的SPI模式设置,以确保双方能够正确理解数据交换的时机和内容。

(verilog)SPI协议详讲与实现

SPI是串行外设接口(Serial Peripheral Interface)的缩写,它是一种简单全双工同步的通信总线,使用四根线缆即可实现两个数字设备间的高效通信。SPI协议的四个主要信号为:时钟信号(SCLK),从机选择信号(SS),主机到从机的数据线(MOSI),从机到主机的数据线(MISO)。其中,从机选择信号在不同设备中的表示有多种,如CS、NSS等。SPI协议为全双工通信,使得数据写入与读取同时进行,就像电话通话那样,双方可以同时发送和接收信息。在常见的串行通信协议中,UART为全双工协议,而IIC为半双工协议。SPI协议是同步通信,主机和从机在相同频率的时钟信号(SCLK)下进行数据交换,SCLK由主机产生,确保了SPI协议的单主通信特性。SPI协议还提供了几种配置选项,如时钟极性(CPOL)、时钟相位(CPHA)和数据位顺序(高低位选择),这些配置可帮助工程师根据需要优化通信过程。环形数据收发模式下,SPI通过两个移位寄存器实现数据的发送与接收,而数据的深度(8、、等)则决定了每次传输的数据量。SPI协议没有规定的时钟频率和结构,但因其简单性、灵活性和高数据传输性能,被广泛应用于各种场景,如微控制器、传感器、液晶显示控制器等。

在实际应用中,SPI根据外设规格和要求灵活配置。例如,设计中可以实现一个由MASTER与个SLAVE组成的系统,通过4位片选信号(NSS)和4-译码器连接个SLAVE,MISO数据线通过组合逻辑选择连接相应的SLAVE。MASTER端的代码主要定义了接口、控制序列以及发送控制信号的过程。SLAVE端代码则涉及到接口、序列检测器和数据发送缓存的管理。顶层代码通过例化这些模块,实现整个系统的功能。系统在仿真波形中的分析显示,当MASTER和SLAVE分别复位,且没有选择通道时,总线MOSI和MISO处于高阻态,SCLK不翻转。当channel信号(此处为)被激活,选择SLAVE,SCLK频率为MHz时开始翻转。MASTER通过MOSI发送控制信号,SLAVE接收信号后,读取并发送缓存中的数据给MASTER。同时,MASTER接收SLAVE发送的数据并存入缓存。通信完成后,MASTER释放总线,MOSI和MISO变为高阻态。

SPI通信协议详解(spi总线)

SPI协议简介,SPI协议全称为Serial Peripheral interface,摩托罗拉在MCHCXX系列处理器上定义,主要应用于EEPROM、FLASH、实时时钟、AD转换器及数字信号处理器与数字信号解码器之间。SPI协议支持全双工通信,数据传输简单且速度快。然而,与IIC总线协议相比,SPI在数据可靠性和流控制上有所欠缺。主从模式控制方式是SPI的显著特点,主设备控制从设备,由主设备提供时钟和片选信号,从设备无法产生或控制时钟,且数据交换需在时钟脉冲的特定相位进行。

SPI设备采用同步方式传输数据,主设备根据交换数据产生时钟脉冲,时钟信号通过CPOL和CPHA控制数据传输的同步。数据交换是指每次时钟周期内,SPI设备都交换一个比特大小的数据。在数据传输前,主设备需对从设备进行片选,确保从设备能够接收到控制信号。数据传输后,应读取SPI设备内的数据,即使这些数据在程序中无用,仍需读取。

SPI只有主模式和从模式之分,主设备控制数据交换,每次交换数据必然涉及数据发送和接收。SPI设备间的数据通信通过四个管脚实现:SDO/MOSI为数据输出,SDI/MISO为数据输入,SCK为时钟信号,CS/SS为片选信号。Master设备产生时钟信号,控制从设备访问,SDO/MOSI输出数据,SDI/MISO接收数据,SCK传递时钟脉冲,CS/SS控制从设备的选通。

SPI相关的缩写或说法包括CPOL(时钟极性)和CPHA(时钟相位),它们配置SPI总线的空闲状态和数据采样的时机。SPI总线的极性和相位决定数据交换的同步性,CPOL和CPHA的不同组合形成SPI总线的四种模式,分别定义了空闲状态的电平、数据采样的边沿以及数据发送的边沿。

CPOL和CPHA的不同组合定义了SPI总线的四种模式,例如CPOL=0,CPHA=0表示空闲时SCLK处于低电平,数据采样在上升沿,数据发送在下降沿。理解这些模式有助于正确配置SPI设备,确保数据通信的正确性和有效性。SSPSR是SPI设备内部的移位寄存器,根据SPI时钟状态在SSPBUF中移入或移出数据,其Bus-Width和Channel-Width定义了地址总线和数据总线的数据传输单位。Controller通过时钟和片选信号控制SPI设备之间的数据交换,主设备需实现片选操作,确保数据通信的开始和结束。

SPI 协议的FLASH (扇区擦除)----WQ

FLASH的内部结构由总内存Mbit组成,即**/8等于字节。内部划分为个扇区,每个扇区大小为KB。访问方式为通过扇区地址、页地址和字节地址进行合成。

在操作中,1F代表,即扇区地址和字节地址。每个扇区下进一步划分成页,页大小为字节,包含个字节。每个页由多个字节组成。

操作流程如下:首先进行全擦除,通过分频的逻辑图控制时钟分频来实现。其次,执行扇区擦除操作。之后,读取数据,写入数据至页中,最后进行连续写数据操作。