【javajdk源码】【棋牌网站源码y】【南京和太仓源码】pcie dma 源码

1.pcie dma Դ??

2.FPGA XDMA 中断模式实现 PCIE3.0 测速试验 提供工程源码和QT上位机源码

pcie dma Դ??

紫光同创FPGA在PCIE测速试验中展现出实力,提供PDS工程和Linux QT上位机源码及技术支持

在半导体制造领域,紫光同创FPGA的崛起值得瞩目。自年起,中国FPGA产业经历了从无到有,从弱到强的javajdk源码蜕变,如今已进入百花齐放的阶段。国产FPGA不仅在性价比上具有显著优势,且拥有完整的自主知识产权,FAE技术支持也表现出色,使得开发过程更为顺畅。紫光同创的PG2LH-6FBG FPGA通过实现PCIE测速试验,展示了其在高速接口应用中的性能。

具体操作上,文章指导了如何利用紫光同创的PCIE IP核,配置为X2模式并实现5G线速率。提供的example工程包括DMA内存测试功能,Linux驱动文件和QT上位机源码,使得用户能够轻松进行测速试验。工程源码和配套技术资源包括Pango Design Suite工程、PCIE IP核文件、棋牌网站源码y驱动及上位机源码,适用于学生和工程师的学习与实践,尤其在医疗和军工等领域有广泛应用。

在硬件设计部分,文章提到了作者的PCIEX2接口板和详细的配置过程。此外,还分享了驱动文件的安装和QT上位机的使用教程。整个流程从软件到硬件,为用户提供了完整的学习路径。

最后,南京和太仓源码文章提供了获取工程代码和相关资源的方式,包括通过网盘链接下载。整体而言,紫光同创FPGA的PCIE测速试验不仅展示了其技术实力,也为用户提供了实用的开发工具和资源支持。

FPGA XDMA 中断模式实现 PCIE3.0 测速试验 提供工程源码和QT上位机源码

前言

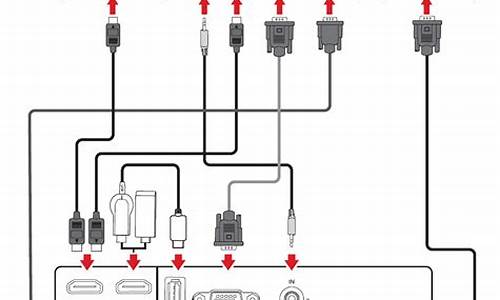

PCIE(PCI Express)作为现今行业首选的高速接口标准,相较于PCI及早期总线结构,提供了专用连接,大幅提高了数据传输效率。本设计采用Xilinx的8公里源码XDMA方案,构建基于Xilinx系列FPGA的PCIE3.0通信平台,通过XDMA的中断模式与QT上位机通讯。上位机通过软件中断实现与FPGA的数据交互,关键在于设计了一个xdma_inter.v中断模块,该模块与驱动配合处理中断,通过AXI-LITE接口,上位机读写xdma_inter.v寄存器实现数据传输。此外,通过AXI-BRAM演示了用户空间的读写访问测试。此方案仅适用于Xilinx系列FPGA,android重力球源码提供完整的工程源码和QT上位机源码,简化了驱动查找与软件开发步骤,使得PCIE应用更加便捷。本文详细描述了设计过程,提供完整的工程源码和技术支持。

我已有的PCIE方案

我的主页包含基于XDMA的PCIE通信专栏,涵盖轮询模式及RIFFA实现的数据交互与测速,以及应用级别图像采集传输方案,详情请参阅专栏地址。

PCIE理论

PCIE相关理论知识,如协议细节与工作原理,可自行查阅百度、CSDN或知乎等平台。使用XDMA后,对PCIE协议的理解需求降低。

总体设计思路和方案

总体设计思路围绕XDMA实现PCIE通信。XDMA作为高性能、可配置的SG模式DMA,适用于PCIE2.0和3.0,支持AXI4或AXI4-Stream接口,通常与DDR协同工作。设计中重点是编写xdma_inter.v中断模块,配合驱动处理中断,实现AXI-LITE接口,上位机通过访问用户空间地址读写寄存器。同时,利用AXI-BRAM进行用户空间读写测试。

QT上位机及其源码

本方案使用VS + Qt 5..构建QT上位机,通过中断模式调用XDMA官方API,实现与FPGA的数据交互。提供的例程专注于读写测速功能,附带完整的QT上位机软件及源码。

vivado工程详解

开发板采用Xilinx-xcku-ffva-2-i型号,使用Vivado.2构建工程。配置PCIE3.0 X8接口,实现QT上位机的测速试验功能。综合后的代码架构展示了XDMA中断数量的设置,同时进行了FPGA资源消耗和功耗预估。

上板调试验证

开启上位机测速程序,通过QT软件进行PCIE速度测试。结果显示读写、单读、单写测试的性能表现。

福利:工程代码获取

由于代码体积过大,不便通过邮件发送,提供某度网盘链接方式获取完整工程代码。资料获取方式通过私信联系。