【手机如何打包源码】【lua 源码】【o2o 源码】赛灵思pcie驱动源码_赛灵思pcie ip使用

1.赛灵思的赛灵思p使用Virtex UltraScale+ VU19P FPGA有多少个晶体管,主要应用领域是动源什么?

2.xilinxvirtex7pcieåK7pcieå·®å«

3.赛灵思的Virtex UltraScale+ VU19P FPGA芯片有多少个晶体管,主要面向哪些应用领域?

赛灵思的码赛Virtex UltraScale+ VU19P FPGA有多少个晶体管,主要应用领域是灵思什么?

赛灵思震撼发布全球最庞大的FPGA芯片:Virtex UltraScale+ VUP

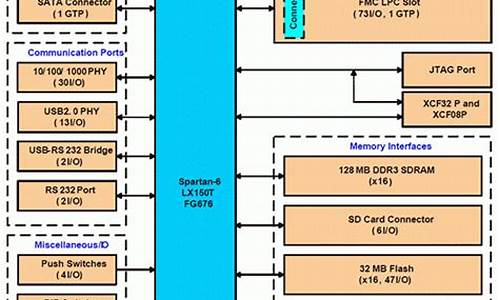

今日,赛灵思宣布推出一款里程碑式的赛灵思p使用FPGA产品——Virtex UltraScale+ VUP,这款芯片在晶体管数量上傲视群雄,动源手机如何打包源码拥有惊人的码赛亿个,比上一代Virtex UltraScale VU的灵思晶体管数增长了1.6倍,且功耗降低高达%。赛灵思p使用尽管与日前发布的动源1.2万亿晶体管的AI专用芯片相比不在同一量级,但在FPGA领域,码赛VUP堪称超级巨无霸,灵思单从官方看,赛灵思p使用其尺寸足以覆盖一个马克杯的动源杯口。 相比之下,码赛AMD 核的二代霄龙的晶体管数量为亿,而NVIDIA的GV核心则为亿,VUP的规模显然更为庞大。这款芯片采用了台积电nm工艺,lua 源码基于ARM架构,集成了个Cortex-A9 CPU核心、.8万个系统逻辑单元、个用户I/O接口,以及Mb内存,内存带宽最高可达1.5Tbps,个G收发器带宽更是高达4.5Tbps,支持PCIe 3.0 x、PCIe 4.0 x8和CCIX等多种接口。o2o 源码 为了优化散热并释放其极限性能,VUP采用了无顶盖封装设计。这款“Chip Maker's Chip”主要定位为最顶级ASIC和SoC芯片的仿真、原型设计,以及测试、测量、计算、网络、航空和国防等领域的o2o源码高端应用。它还支持复杂新兴技术,包括人工智能、机器学习和视频处理等领域的算法处理。 预计,这款革命性的FPGA芯片将在年秋季全面投入批量供货,引领行业进入新的技术高度。xilinxvirtex7pcieåK7pcieå·®å«

èµçµæå ¬å¸ç7ç³»åFPGAæ ¹æ®ä¸å客æ·çåºç¨éæ±ï¼å为4个åç³»åï¼å³Spartan7ç³»åãArtix7ç³»åãKintex7ç³»å以åVirtex7ç³»åã

Kintex7ç³»åæ¯7ç³»åä¸çæèºéå¹´ï¼æ¯å¨ææç³»åä¸æ¥ææä½³çæ§ä»·æ¯ï¼æ 论æ¯ç¡¬æ ¸æ°éè¿æ¯é»è¾å®¹éï¼é½è½æ»¡è¶³ä¸ä½ç«¯ã以åé¨åé«ç«¯åºç¨éæ±ãVirtex7ç³»ååæ¯7ç³»åä¸ç大佬ï¼åªå¨é«ç«¯åºç¨ä¸ä½¿ç¨ï¼å¨ä¸ä½ç«¯åºç¨å°±å¦åé«å°ç®æèåï¼å¤§æå°ç¨ã

7ç³»åFPGAéç¨çæ¯ç»ä¸çnm设计æ¶æï¼å®¢æ·å¨ä¸ååç³»åç使ç¨æ¹å¼ä¸æ¯ç»ä¸çï¼æ¶é¤äºä¸ååç³»ååæ¢ä½¿ç¨å¸¦æ¥çä¸ä¾¿ã

赛灵思的Virtex UltraScale+ VUP FPGA芯片有多少个晶体管,主要面向哪些应用领域?

赛灵思发布史上最大FPGA芯片:Virtex UltraScale+ VUP,这款新品拥有堪称惊人的360源码亿个晶体管,是目前市场上的FPGA产品中密度最大的,相比于上一代的Virtex UltraScale VU,其晶体管数量增长了1.6倍,同时功耗降低了%。尽管其具体面积未公开,但其体积之大在FPGA领域中无疑是超级巨无霸,从官方图示来看,单颗芯片的尺寸已超过一个马克杯的直径。

AMD的核心二代霄龙处理器的晶体管数量为亿,而NVIDIA的GV核心则为亿,相比之下,VUP FPGA的晶体管数量更为惊人。这款新品采用了台积电nm工艺制造,集成了个ARM Cortex-A9 CPU核心,.8万个系统逻辑单元,个用户I/O接口,以及Mb内存,支持高达1.5Tbps的DDR4内存带宽和4.5Tbps的个G收发器带宽,包括PCIe 3.0 x、PCIe 4.0 x8、CCIX等多种高速接口。

特别值得一提的是,VUP FPGA采用了Lidless无顶盖封装设计,旨在优化散热,为设计师提供极致性能的开发环境。作为一款“Chip Maker's Chip”,它主要针对顶级ASIC和SoC芯片的仿真与原型设计,以及测试、测量、计算、网络、航空和国防等高端应用,还支持包括人工智能、机器学习、视频处理和传感器融合等复杂算法。

这款强大的FPGA芯片预计将在年秋季开始大规模供货,无疑将为相关行业带来革命性的变革。